Hindawi Complexity Volume 2017, Article ID 8263904, 10 pages https://doi.org/10.1155/2017/8263904

# Research Article

# Understanding the Resistive Switching Phenomena of Stacked Al/Al<sub>2</sub>O<sub>3</sub>/Al Thin Films from the Dynamics of Conductive Filaments

# Joel Molina-Reyes and Luis Hernandez-Martinez

National Institute of Astrophysics, Optics and Electronics, Luis Enrique Erro No. 1, 72840 Tonantzintla, PUE, Mexico

Correspondence should be addressed to Joel Molina-Reyes; jmolina\_molina@hotmail.com

Received 5 May 2017; Accepted 11 July 2017; Published 20 September 2017

Academic Editor: Sundarapandian Vaidyanathan

Copyright © 2017 Joel Molina-Reyes and Luis Hernandez-Martinez. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

We present the resistive switching characteristics of Metal-Insulator-Metal (MIM) devices based on amorphous  $Al_2O_3$  which is deposited by Atomic Layer Deposition (ALD). A maximum processing temperature for this memory device is 300°C, making it ideal for Back-End-of-Line (BEOL) processing. Although some variations in the forming, set, and reset voltages ( $V_{\rm FORM}$ ,  $V_{\rm SET}$ , and  $V_{\rm RESET}$ ) are obtained for many of the measured MIM devices (mainly due to roughness variations of the MIM interfaces as observed after atomic-force microscopy analysis), the *memristor* effect has been obtained after cyclic I-V measurements. These resistive transitions in the metal oxide occur for both *bipolar* and *unipolar* conditions, while the  $I_{\rm OFF}/I_{\rm ON}$  ratio is around 4–6 orders of magnitude and is formed at gate voltages of  $V_{\rm SET}$  and  $V_{\rm SET}$  is observed and is related to combined (a) incomplete dissolution of conductive filaments (made of oxygen vacancies and metal ions) which leaves some residuals and (b) thickening of chemically reduced  $V_{\rm SET}$  and  $V_{\rm SET}$  is important because, by analyzing the macroscopic resistive switching behavior of this MIM structure, we could indirectly relate it to microscopic and/or nanoscopic phenomena responsible for the physical mechanism upon which most of these devices operate.

#### 1. Introduction

Since the invention and experimental demonstration of the memristor (an integrated device with memory-resistance properties, able to correlate electric charge to magnetic flux q- $\varphi$  [1]), several materials in the form of thin dielectric films or solid electrolytes have been tested for these emergent nonvolatile memory devices in order to produce reliable and reversible switching cycles of the resistive state of the oxide. Thin film based materials able to switch from a high resistance state (HRS/OFF) to a low resistance state (LRS/ON) and vice versa are responsible for the typical "pinched hysteresis loops," which are observed during cyclic current-voltage (I-V) measurements of these devices. This has contributed to the development of important applications like nonlinear circuits, chaotic systems, highly dense neural networks, and even neuromorphic computing, where the diffusive dynamics of memristors can be used as synaptic emulators. Nevertheless,

all these highly dynamic applications exploiting the memristor effect do so without considering complex microscopic and nanoscopic phenomena, mainly related to the evolution and migration dynamics of atomic elements within the integrated device. Recently, several Metal-Insulator-Metal structures have shown the ability to switch between these two resistive states (HRS  $\leftrightarrow$  LRS) after promoting resistive switching phenomena (by forming/dissolving conductive filamentary paths in mostly binary oxides) or ion migration mechanisms (by cation or anion species in solid electrolytes) during high electrical stress of the devices [1, 2]. In this sense, Resistive switching Random Access Memory (ReRAM) devices have attracted considerable attention in the recent years due to their superior characteristics for nonvolatile data storage. Some of these advantages are a simple memory structure (usually composed of MIM stacks), deep scalability, ultralow power consumption, fast write/erase speed, and long retention times [3]. Also, even though the precise physics behind

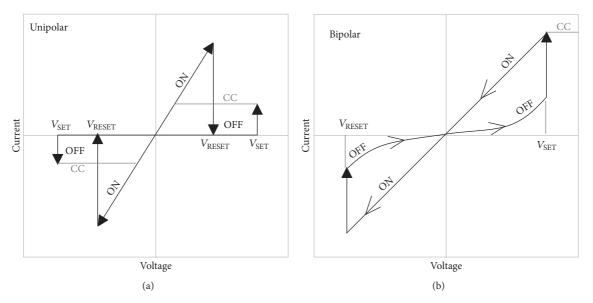

FIGURE 1: I-V diagrams showing the (a) unipolar and (b) bipolar operation modes for ReRAM devices where no dependence of the "pinched hysteresis loops" to frequency is involved (DC conditions). The unipolar mode is able to promote resistive switching using a positive or negative polarity with  $V_{\text{SET}} > V_{\text{RESET}}$  and  $CC_{\text{SET}} < CC_{\text{RESET}}$ .

the operation mechanism is still not fully understood, by using resistive switching and/or ion migration phenomena, there have been some advances in which, for many cases, single and/or multiple filamentary conduction paths can be formed or dissolved in the oxide, thus connecting or disconnecting both metal electrodes and, therefore, giving origin to both LRS and HRS [4, 5]. This is important because a better understanding of the resistive switching phenomena could enable enhanced nonlinear applications like the ones previously described, while also providing better modeling tools for nonlinear devices and systems. ReRAM switching modes can be classified into two groups: unipolar switching and bipolar switching. In unipolar mode, the resistive switching transitions (HRS  $\leftrightarrow$  LRS) of the oxide layer are obtained using the same polarity but different magnitudes of applied bias (while limiting the gate current at two current compliance levels). In bipolar mode, these transitions are obtained using different polarities of applied bias so that typical hysteresis loops in the I-V characteristics (Lissajous curves) are observed [3, 5]. In any case, these resistive switching transitions require specific voltages so that  $V_{\text{SET}}$  and  $V_{\text{RESET}}$  would promote HRS  $\rightarrow$  LRS (ON) and HRS  $\leftarrow$  LRS (OFF) transitions, respectively (see Figures 1(a)-1(b)).

Depending on the MIM structure, an additional forming voltage  $V_{\rm FORM}$  is necessary in order to force the initial HRS  $\rightarrow$  LRS transition and, generally,  $V_{\rm FORM} > V_{\rm SET} > V_{\rm RESET}$ . It is important to consider that, for any operation mode, a limit in the current flowing through the MIM device should be established in order to prevent permanent oxide breakdown and, therefore, losing the memory effect. In the unipolar mode, two different current limits must be used so that during the creation of a conductive path/filament by  $V_{\rm SET}$  a low current compliance limit  ${\rm CC}_{\rm SET}$  would enable a controlled formation of these conductive paths, while a higher current

compliance limit CC<sub>RESET</sub> would be required for the dissolution of this conductive path/filament by  $V_{\rm RESET}$  (much like the breakdown of a fuse after passing a large current density through it). Usually, more reproducible characterization of ReRAM devices based on MIM structures would require that  $V_{\rm FORM} > V_{\rm SET} > V_{\rm RESET}$  and  ${\rm CC}_{\rm RESET} > {\rm CC}_{\rm SET}$  and doing so by also using specific time-dependent waveforms as polarization sources so that the time-dependent properties of these devices could also be extracted (like the well-known poor frequency dependence of experimental memristors, where the total area of the pinched hysteresis loops decreases with the frequency of applied bias). On the other hand, it is known that, during the reset process in the unipolar switching mode, a large current flow (needed to dissolve an already formed conductive filament (CF)) would produce localized Joule heating at this conductive filament which, in turn, could lead to its partial dissolution and, therefore, to a large amount of residuals around it (oxygen vacancies and/or metal ions) [6, 7]. The amount and type of these residuals are largely dependent on the CC levels as well as the velocity during the voltage sweeps needed for the cyclic HRS ↔ LRS transitions. The residual combination of metal atoms/complexes/compounds within the remaining oxide could contribute to higher leakage currents as well as electrical instabilities (like charge trapping-detrapping events or a gradual reduction in  $V_{\rm SET}$ ) of ReRAM devices upon more switching cycles, leading to narrowing of the resistive window and, thus, lower endurance. Here, we monitor the gradual reduction in  $V_{\rm SET}$  after the 5 initial switching cycles of an Al/Al<sub>2</sub>O<sub>3</sub>/Al structure (unipolar operation) and we relate this reduction of  $V_{\rm SET}$  to residuals of aluminum ions (during partial dissolution of the conductive filament by a large current flow) which act as trap centers that lower the energy barrier of Al<sub>2</sub>O<sub>3</sub> while decreasing the set

voltage (25th International Conference on Amorphous and Nanocrystalline Semiconductors).

## 2. Materials and Methods

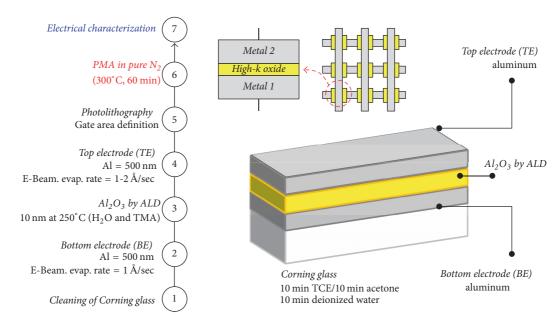

For MIM device fabrication, stacked Al/Al<sub>2</sub>O<sub>3</sub>/Al thin films were sequentially deposited on previously cleaned Corning glass slides and standard photolithography steps were used for gate pattern definition, while the whole stack is finally annealed in N<sub>2</sub> at 300°C. Initially, all glass slides were cleaned by sequential immersion in trichloroethylene (TCE) and acetone (10/10 min) within an ultrasonic vibrator. This is followed by rinsing in deionized water (DI water) by 10 min and the slides are gently dried using an ultrahigh purity N<sub>2</sub> blow. Aluminum is used as bottom and top electrode (BE/TE) for the MIM device. The BE/TE consist of aluminum layers each with 500 nm in physical thickness and they were deposited by E-beam evaporation (Temescal BJD-1800 from Edwards) under ultrahigh vacuum conditions using a deposition rate of 1-2 Å/sec. Al<sub>2</sub>O<sub>3</sub> with 20 or 10 nm in thickness were deposited on the BE by thermal ALD at 250°C (Savannah S100 from Cambridge NanoTech) using H<sub>2</sub>O and Trimethylaluminum (TMA) as chemical precursors for the oxygen and aluminum elements of  $Al_2O_3$ . Also, a thinner  $Al_2O_3 = 6$  nm was used in Metal-Insulator-Semiconductor (MIS) structures in order to confirm the high electrical quality of this metal oxide via *I*-V and C-V measurements. The ALD process was performed at 250°C/200 mTorr of temperature/pressure for all 200, 100, or 60 deposition cycles of Al<sub>2</sub>O<sub>3</sub> deposition. All these samples were quickly introduced into the e-beam evaporator after ALD of Al<sub>2</sub>O<sub>3</sub>. There, the evaporation chamber was vacuumed down to  $1 \times 10^{-7}$  Torr in order to minimize the exposure time of the Al<sub>2</sub>O<sub>3</sub> surfaces to atmospheric oxygen or any other contaminant of the clean room. Standard photolithography steps followed after complete metallization of these MIM devices. For this, all samples were covered with positive photoresist using standard spinning/baking conditions and exposed to an UV system (Karl Suss MA6) in order to transfer gate patterns to the TE. Gate capacitor areas of  $36 \times 10^{-6}$  cm<sup>2</sup> and  $64 \times 10^{-6}$  cm<sup>2</sup> were used for the MIS and MIM devices, respectively. After gate pattern definition, only the Al/Al<sub>2</sub>O<sub>3</sub>/Al/Glass (MIM) structures were annealed in pure N<sub>2</sub> (99.999% purity) at 300°C in order to promote densification of Al<sub>2</sub>O<sub>3</sub> along with interfacial layer development of this metal oxide with BE/TE (nonstoichiometric Al<sub>x</sub>O<sub>y</sub> interfacial layers are expected). The complete fabrication procedure is very simple (see Figure 2), while the maximum processing temperature is 300°C. A low thermal budget in the processing of these devices makes them ideal for their integration in the BEOL stages of an integrated circuit, thus further increasing the integration density of memory devices.

# 3. Results and Discussion

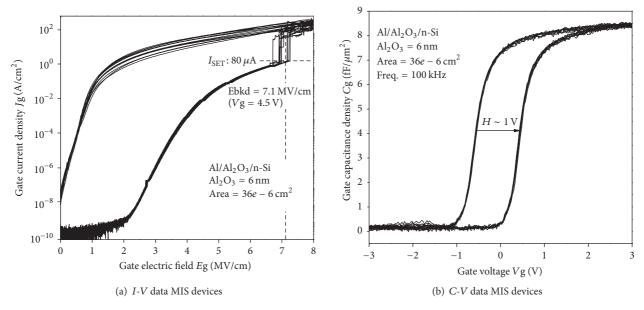

Given the thin physical thickness for  $Al_2O_3$  used in the MIM structures (20 and 10 nm), we have electrically characterized MIS devices in which an even thinner  $Al_2O_3 = 6$  nm has been deposited on silicon by using the same ALD conditions (without thermal annealing). Therefore, by using a silicon

surface with very low atomic surface roughness (as compared to a metallic bottom electrode), we are able to assess the intrinsic electrical quality of Al<sub>2</sub>O<sub>3</sub>. Figures 3(a)-3(b) show the I-V and C-V characteristics of several Al/Al<sub>2</sub>O<sub>3</sub>/n-Si MIS devices in which good uniformity is observed after measuring at least 15 MIS devices for each data set. The I-V data (normalized to gate area and oxide thickness) show a high electric field required for oxide breakdown (Ebkd = 7.1 MV/cm) (under accumulation or substrate injection condition), while the resistivity window before and after hard breakdown can be as high as 10 orders of magnitude (for  $Eg \leq 2 \,\mathrm{MV/cm}$ ). The C-V data, on the other hand, show a large hysteresis window H (measured at flat-band voltage) which is characteristic of a bad Al<sub>2</sub>O<sub>3</sub>/Si interface, so that several defects (from a large density of dangling bonds to chemical reduction of Al<sub>2</sub>O<sub>3</sub> into AlSi<sub>x</sub>O<sub>y</sub> silicates) would promote higher densities of charge trapping.

Also, moderate capacitance in accumulation turns into a dielectric constant of  $k \sim 6$ , a relatively low value compared to what is expected for bulk  $\mathrm{Al_2O_3}$  ( $k \sim 9$ ) and yet the good uniformity in the C-V data is again observed for all measured MIS devices. For the MIM structures, we could expect some deviations from I-V data in particular, since large defects are found at the interfaces of  $\mathrm{Al_2O_3}$  with both the bottom and top metallic electrodes.

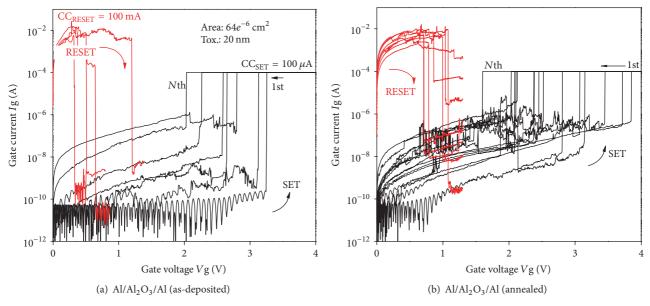

In order to show the cyclic resistive switching characteristics of the metal oxide film, thicker  $Al_2O_3 = 20 \text{ nm}$ (deposited by ALD with the same conditions) was used in an Al/Al<sub>2</sub>O<sub>3</sub>/Al/Glass stacked structure and electrically characterized before and after the final thermal treatment applied to the device. Figures 4(a)-4(b) show the resistive switching characteristics (in unipolar mode) of this structure. Even though the gate current levels are increased for the annealed sample (especially during the HRS condition), we notice that different current compliance levels are needed for both samples whenever we promote a transition from the HRS to the LRS condition and vice versa. For this thicker  $Al_2O_3$ , the limit in  $CC_{SET}$  is set to 100  $\mu$ A, whereas  $CC_{RESET}$  = 100 mA; both are large current densities flowing through the oxide layer and that would increase the chances for leaving large amount of residuals (after the RESET condition which produce localized Joule heating in the previously formed conductive filament) in the form of a high density of oxygen vacancies (neutral or charged) and/or metal ions. We also observe that some electrical instabilities in the gate current Ig do occur after the initial resistive switching cycles, where the as-deposited and annealed samples produce 8 and 16 cycles (HRS  $\leftrightarrow$  LRS transitions), respectively. These electrical instabilities are due to charge trapping-detrapping events that, later, are related to conduction mechanisms, where trapenergy levels are responsible for these phenomena.

The conduction mechanisms initially considered for modeling these gate tunneling currents were Ohmic Conduction (OC), Thermionic Emission (TE), Space-Charge Limited Current (SCLC), Trap-Assisted Tunneling (TAT), Poole-Frenkel (PF), and Fowler-Nordheim (FN). After linear fitting of the experimental *I-V* data (only for the HRS condition just before oxide breakdown or conductive filament formation),

FIGURE 2: Process flow for fabrication of  $Al/Al_2O_3/Al$  stacked structures using a maximum temperature of  $300^{\circ}$  C, ideal for BEOL processing. Traverse cut of an ideal MIM device (where M1 = M2 = aluminum) as well as possible MIM arrays that could be densely integrated within the BEOL stages of an integrated circuit.

FIGURE 3: Electrical characteristics of MIS devices based on thinner  $Al_2O_3 = 6$  nm and without thermal annealing. Outstanding uniformity is observed for both (a) I-V and (b) C-V data after testing at least 15 different MIS devices for each measurement. This confirms the good quality of ALD method for deposition of thin  $Al_2O_3$ .

PF and FN mechanisms were confirmed as the main conduction models with specific trap/barrier energy levels  $\Phi_t/\Phi_B$  for  $\mathrm{Al_2O_3}$  [8]. This  $\Phi_t$  level (PF model) is often associated with some defects and/or impurities in the oxide layer and this makes sense if we consider that some residuals could remain after partial dissolution of the conductive filament. This would impact the reliable operation of a ReRAM device because it will also produce a gradual decrease in the voltage needed for a new SET operation as will be shown later. Also,

it is important to notice that a broad resistivity window between the HRS and LRS is obtained for these samples, where 4-6 orders of magnitude secure high endurance during continuous I-V resistive cycling of these devices.

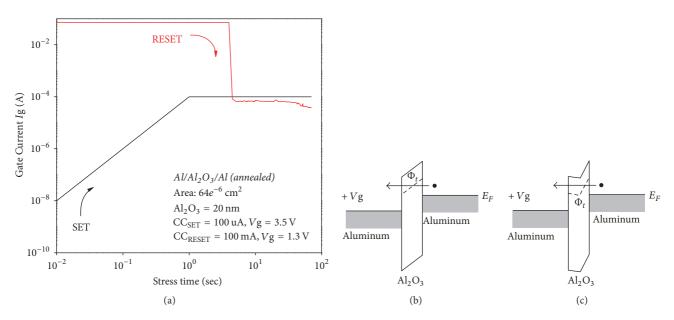

For the annealed Al/Al<sub>2</sub>O<sub>3</sub>/Al/Glass MIM device (with thicker Al<sub>2</sub>O<sub>3</sub> = 20 nm), monitoring of the gate current Ig with time during a constant gate voltage Vg applied (in the two resistive states HRS and LRS) produces the results shown in Figure 5(a). Initially, large  $V_{\rm SET}$  = 3.5 V forces Ig to

FIGURE 4: Resistive switching of Al/Al<sub>2</sub>O<sub>3</sub>/Al stacked structures (using thicker Al<sub>2</sub>O<sub>3</sub> = 20 nm) for the (a) as-deposited and (b) annealed devices in N<sub>2</sub> at 300°C conditions. The unipolar mode for resistive switching is obtained after using  $CC_{SET} = 100 \,\mu\text{A}$  and  $CC_{RESET} = 100 \,\text{mA}$ . A large resistivity window is also observed for both samples.

FIGURE 5: (a) Gate current versus stress time for  $Al/Al_2O_3/Al$  structure during the SET and RESET conditions. A gradual increase in Ig during the SET condition is evidence of positive charge trapping in the MIM device. Ideal energy band diagrams for the MIM structure under positive bias and where (b) PF tunneling conduction through  $\Phi_t$  is initiated; (c) a large density of trapped positive charge modifies the energy gap of  $Al_2O_3$ .

reach the LRS almost immediately (formation of conductive filament) and it is only limited by  $CC_{SET}=100~\mu A$ . We notice a gradual increase in Ig with time until  $CC_{SET}$  is reached and this is related to continuous trapping of positive charge [9] in the bulk and/or interfaces of  $Al_2O_3$  (enabled by a PF model with a given  $\Phi_t$  level; see Figure 5(b)). It is thought that a high density of trapped positive charge would be able to modify

the energy barriers of  $Al_2O_3$  during tunneling of carriers [9–12] (see Figure 5(c)), so that Ig conduction enhances while progressively reducing  $V_{\rm SET}$ . For dissolution of the conductive filament, large  $CC_{\rm RESET}=100\,{\rm mA}$  is required (producing Joule heating) and this produces a sudden decrease in gate current Ig which, in this case, is obtained after the first seconds of stressing bias.

FIGURE 6: Resistive switching for annealed Al/Al<sub>2</sub>O<sub>3</sub> (10 nm)/Al stacked structures. (a) Bipolar mode with CC = 100 mA and (b) unipolar mode with CC<sub>SET</sub> =  $100 \,\mu$ A. The  $I_{\rm OFF}/I_{\rm ON}$  ratio for these structures is  $10^4$ – $10^6$  for both operation modes. For the unipolar mode, a decrease in  $V_{\rm SET}$  is observed during continuous resistive switching.

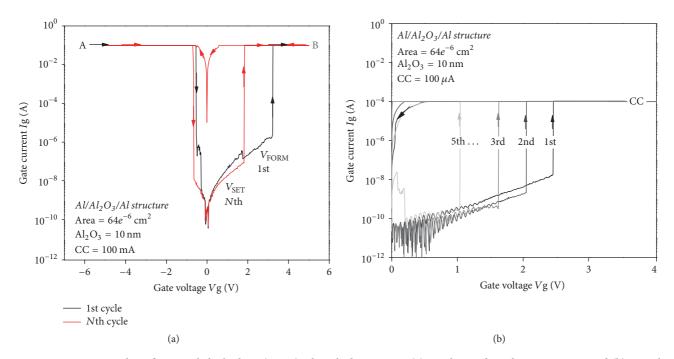

Having a large density of trapped positive charge (after the partial dissolution of a conductive filament) will have a profound impact on the endurance characteristics of a ReRAM device. For this, we will examine the electrical characteristics of annealed Al/Al<sub>2</sub>O<sub>3</sub>/Al/Glass stacked structures having thinner  $Al_2O_3 = 10$  nm. Figure 6(a) shows the first breakdown voltage (forming voltage  $V_{\text{FORM}}$ ) of the memory cell which is larger than the  $N{\rm th}$  set voltage ( $V_{\rm SET}$ ) and also the initial current in the HRS is much smaller compared to the current in the LRS as expected. These *I-V* characteristics correspond to the bipolar switching mode, where a double sweep of voltage (using both polarities) is applied to the same MIM device and I-V hysteretic loops are obtained, while the maximum current is limited to  $CC = 100 \, \text{mA}$ . It is important to notice that limiting the maximum current flowing through the device helps to prevent permanent damage of the oxide and therefore more resistive switching cycles could be obtained. For this MIM device,  $V_{\text{FORM}} > V_{\text{SET}}$ and the  $I_{\rm OFF}/I_{\rm ON}$  ratio is ~6 orders of magnitude, a large resistivity window able to promote higher endurance during cyclic ReRAM operation. Here, the Nth cycle is the 8th I-V cycle and the gate current at this 8th HRS is lower compared to the 1st HRS, which indicates trapping of negative charge. Whether it was a positive or negative charge, it is clear that a high density of trapped charge is able to decrease  $V_{\rm SET}$  in both modes.

For the same MIM structure in the unipolar mode, Figure 6(b) shows that the first transitions to a LRS condition cause a progressive reduction in  $V_{\rm SET}$  (during sequential switching from HRS to LRS, up to 5 cycles) in the same device. Here, the corresponding HRS  $\leftarrow$  LRS transitions are

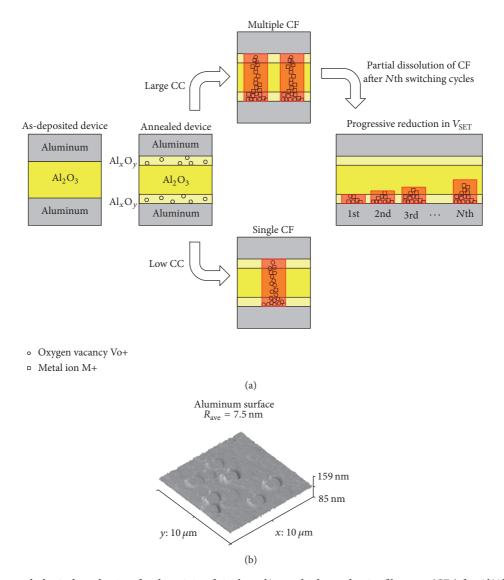

not shown for clarity purposes. Again, even though a large resistivity window is also obtained (4–6 orders of magnitude), a progressive reduction in  $V_{\text{SET}}$  will compromise both the endurance and other reliability parameters for these memory devices. The exact physical origin for this reduced  $V_{\text{SET}}$  is out of the scope of this work but there is plenty of evidence pointing to (1) the chemical reduction of Al<sub>2</sub>O<sub>3</sub> into offstoichiometric Al<sub>x</sub>O<sub>y</sub> after oxygen scavenging by the BE/TE metal layers [13, 14] (thus decreasing the total dielectric constant) and/or (2) metal migration from the BE/TE into Al<sub>2</sub>O<sub>3</sub> so that a localized conductive nanofilament (formed by a SET process) could be partially dissolved by a RESET process [6, 7], thus reducing both the effective oxide thickness and the next  $V_{\text{SET}}$  needed for a new HRS  $\rightarrow$  LRS transition (see Figure 7(a)). Since these memory devices can have two types of switching modes (unipolar and bipolar), each switching mode will mainly depend on the applied bias conditions, on the magnitude of the compliance currents that will limit the total current after breakdown, and, more importantly, on the energy required to transport electronic and/or ionic (oxygen vacancies and metal ions) charge for cyclic formation and rupture of conductive filaments. It is important to notice that, for both the bipolar and unipolar modes, the minimum current compliance during continuous resistive switching of this device is set to  $CC \ge 100 \,\mu\text{A}$ . It has been recently demonstrated that the level of CC fixed for memory switching is quite important for transitioning between two resistive states of a binary metal oxide [6, 7]. At lower CC < 10  $\mu$ A, the switching occurs due to a conductive path formed mainly by charged oxygen vacancies [Vo<sup>+</sup>], while for CC >  $10 \,\mu\text{A}$ , the conduction path is formed by metal ions [M<sup>+</sup>] that

FIGURE 7: (a) Proposed physical mechanism for the origin of single and/or multiple conductive filaments (CFs) for  $Al/Al_2O_3/Al$  structure during the SET process (depending on the current compliance limit) and the effect that partial dissolution of this previously formed CF has on the progressive reduction of  $V_{SET}$ . For larger CC, multiple formation of CFs should be expected, with their composition being mostly based on metal ions  $[M^+]$ . (b) Average surface roughness of the BE (after AFM) showing large surface roughness which is close to the physical  $Al_2O_3$  thickness of the MIM device. High surface roughness would promote local electric-field enhancements.

diffuse or migrate from the metal electrodes (BE/TE) into the oxygen vacancy-rich oxide defect network [15–17]. This is very important, since, depending on the type of species forming the conductive filament (Vo $^+$  or M $^+$ ), any residual left after dissolution of the conductive filament (RESET process) would make the detrapping process from a shallow/deep trap-energy level easier/harder, thus affecting the resistivity windows, endurance, and other reliability issues. Of course, a more precise estimation of the current needed to induce Vo $^+$  or M $^+$  based formation of conductive filaments would be normalizing Ig to smaller device areas or, even better, integrating the injected charge with time [18, 19] because, due to highly different oxide thicknesses, very different current levels would be required. Nevertheless, the oxide thickness regime in our samples is in concordance with the migration

thermodynamics for Vo<sup>+</sup>/M<sup>+</sup>, described quite recently [6, 7]. In our samples, the I-V data of Figure 6 already show that CC is set to 100 mA and 100  $\mu$ A for the bipolar and unipolar switching modes, respectively, thus suggesting that the main species forming the conductive filament (by a SET process) are based on metal ions [M<sup>+</sup>] which, in this case, would be some specific oxidation states of aluminum (the same metal material for both the BE and TE). A simplified model showing the physical mechanisms behind a progressive reduction in  $V_{\text{SET}}$  as well as the surface roughness of the BE is illustrated in Figures 7(a)-7(b). During formation of single/multiple conductive filaments, not only the current compliance but also the surface roughness at the metal/oxide interfaces are important, since this would lead to local electric-field enhancements and then early breakdown [20, 21].

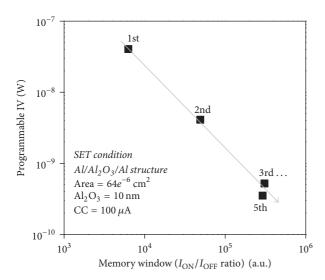

FIGURE 8: Based on the data of Figure 6(b), the power needed to promote continuous resistive switching of that MIM structure is reduced, while the memory window ( $I_{\rm ON}/I_{\rm OFF}$  ratios) increases. Even though these are desirable characteristics for a ReRAM device, this behavior is a consequence of the progressive reduction in the  $V_{\rm SET}$  parameter which, in turn, will compromise endurance and the general reliability of these memory devices.

Figure 7(a) suggests that, by using large CC, generation of a single broad conductive filament or generation of more than one conductive filament occurs. Generation of single or multiple conductive filaments is in the end promoted by the total current flowing through the device. We also notice that, by using a sufficiently large CC limit during each switching cycle, a partial dissolution of the CF would mostly leave a high density of metal ions (close to the biased anode) which then results in the progressive reduction of  $V_{\text{SET}}$ (as observed in Figure 6(b)). Figure 7(b) shows the surface morphology of the first aluminum layer which was used as bottom electrode in the Al/Al<sub>2</sub>O<sub>3</sub>/Al structure. The average roughness for this aluminum layer is 7.5 nm (which could be related to formation of stacking faults during evaporation of this metal) and since the physical thickness of  $Al_2O_3 = 10$  nm, reducing this severe surface roughness is critical in order to enhance the reproducibility of hysteretic *I-V* characteristics. Therefore, we could relate the observed variations in  $V_{\rm FORM}$ ,  $V_{\rm SET}$ , and  $V_{\rm RESET}$  of Figures 4(a)-4(b) to variations in the physical thickness of the effective oxide, since the roughness [22] at the metal/Al<sub>2</sub>O<sub>3</sub> interfaces is almost of the same physical thickness as observed after atomic-force microscopy.

Figure 8 shows the power  $(V_{\text{SET}} \cdot I_{\text{SET}})$  needed to promote the HRS  $\rightarrow$  LRS transitions already observed in Figure 6(b) versus the memory window  $(I_{\text{ON}}/I_{\text{OFF}})$  ratios) therein obtained. A seemingly desirable tendency is observed, where, for 5 continuous resistive switching cycles (unipolar mode), less power is required to produce these transitions, while the memory window is also increased. This behavior, however, is due to progressively reduced  $V_{\text{SET}}$  which, in turn, will severely compromise the endurance and the long-lasting performance of these devices.

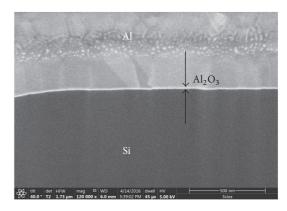

FIGURE 9: Scanning electron microscopy image for  $Al/Al_2O_3/Si$  structure ( $Al_2O_3 = 20$  nm, annealing in  $N_2$  at  $300^{\circ}C$ ) after FIB preparation of a traverse-cut face (using secondary electrons of an intralens detector for morphology imaging). A smooth transition between all materials is observed, while the polycrystalline nature of the metal electrode is also visible.

Figure 9 shows the scanning electron microscopy image (secondary electrons using an in-lens detector) of  $Al_2O_3$ -based MIS device ( $Al_2O_3 = 20 \, \text{nm}$ , annealing in  $N_2$  at  $300^{\circ}\text{C}$ ) in which the ultralow atomic surface roughness of the silicon substrate is used in order to show a relatively smooth transition in the morphology and composition of all the materials used for the stacked structure (seen as a sharp difference in the contrast for all films).

The image shows the "curtaining effect" or ripple formation after focused-ion beam (FIB) preparation [23] of a specific face of this MIS device. Because of the sputtering action of the ion beam, the FIB can be used to locally remove or mill away material (exposing the desired face and its interfaces) while getting surface roughening and shadowing effects due to heavy ion bombardment. Although it is difficult to confirm the chemical reduction of  $Al_2O_3$  into  $Al_xO_y$  after annealing (as schematically illustrated in Figure 7(a)), we can observe the high uniformity of the Al<sub>2</sub>O<sub>3</sub> film after thermal ALD and even the polycrystalline nature of the aluminum electrode which is the material used for the BE and TE in our MIM devices. This is important given the relatively large gate area for these MIM devices (80  $\mu$ m × 80  $\mu$ m), where intrinsic defects directly related to the resistive switching of the highk layer could be masked by extrinsic defects whenever larger areas are under electrical characterization [24–26].

A full understanding of the complex resistive switching phenomena is still a work in progress to which many research labs across the globe have actively contributed so that, by now, microscopic and nanoscopic details related to migration dynamics of atomic elements within stacked MIM structures have emerged. This is quite important since it could contribute to a better definition of the "memristor effect" which by now is still limited to the basic memristor fingerprints [27–29] able to identify a memristive device:

(1) The device must exhibit a "pinched hysteresis loop" in the voltage-current plane for any bipolar periodic signal excitation. This "pinched hysteresis loop" must

converge and cross the origin of this voltage-current plane.

- (2) The pinched hysteresis loop area should decrease monotonically as the excitation frequency increases.

- (3) The pinched hysteresis loop should shrink to a single-valued function when the frequency tends to infinity, which is similar to turning a memristor into a common resistor, where well-defined linear *I-V* dependence is observed.

Nevertheless, this work tries to identify and correlate some issues that occur simultaneously in MIM devices during cyclic resistive switching measurements: (a) the origin of variations in the resistive switching phenomena of Al/Al<sub>2</sub>O<sub>3</sub>/Al devices in both the bipolar and unipolar modes, (b) the modeling of a mechanism responsible for these variations (combining physical, chemical, and electronic phenomena) and whose more accurate details, occurring at the nanoscopic level, have been demonstrated for even higher dielectric constant materials like HfO<sub>2</sub> [24-26, 30, 31], and (c) the connection of the former points from the perspective of the formation/dissolution of conductive filaments. All these issues are of the utmost importance in order to provide a more precise physical explanation regarding the operation mechanism of ReRAM devices and, therefore, enabling the development of accurate electrical models (not only for the DC regime but also for frequency-dependent conditions) that could accelerate the research and application of nonlinear phenomena with these memristive materials and devices.

#### 4. Conclusions

MIM based ReRAM devices (using symmetric Al/Al<sub>2</sub>O<sub>3</sub>/Al structures) have been fabricated at low processing temperatures and the resistive switching effect has been observed for both the bipolar and unipolar operation modes which are dependent on the amount of electrons tunneling through the device. For cyclic ReRAM operation,  $V_{\text{FORM}} > V_{\text{SET}} > V_{\text{RESET}}$ was found and a relatively large  $I_{\rm OFF}/I_{\rm ON}$  ratio of 4–6 orders of magnitude is useful for higher endurance. In the unipolar switching mode and by measuring several resistive switching cycles in the same sample,  $V_{\rm SET}$  is progressively reduced and that might be related to a combined mechanism of (a) incomplete dissolution of conductive filaments (made of oxygen vacancies and, mostly, metal ions) which leaves some residuals close to the anode and (b) thickening of chemically reduced Al<sub>2</sub>O<sub>3</sub> during localized Joule heating. Also, even though high uniformity of thicker Al<sub>2</sub>O<sub>3</sub> films is observed in MIS devices after SEM imaging, the surface roughness of the aluminum-based bottom electrode (after AFM analysis) is close to the physical thickness of Al<sub>2</sub>O<sub>3</sub> itself, thus compromising the performance and general reliability of these MIM devices by localized electric-field variations. Nevertheless, these samples have shown the memristor effect while using low-temperature processing and standard materials used in the BEOL stages of an integrated circuit. By optimizing the physical and processing parameters of this structure, vertical integration of dense memory arrays using MIM structures

could be implemented at BEOL processing in order to obtain denser, smarter, and more efficient integrated circuits. Given the importance of memristive devices (also memcapacitive and meminductive elements) for modeling nonlinear phenomena, experimental evidence relating resistive switching behavior to microscopic and nanoscopic details of conductive filament formation is necessary in order to use better models for the analysis, design, and simulation of memristor-based circuits (with analog, digital, logic, neuromorphic, secure communications and several other applications).

#### **Conflicts of Interest**

The authors declare that there are no conflicts of interest regarding the publication of this paper.

# Acknowledgments

This work was fully supported by the National Council of Science and Technology (CONACYT), Mexico.

## References

- [1] D. B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams, "The missing memristor found," *Nature*, vol. 453, pp. 80–83, 2008.

- [2] J.-J. Ke, Z.-J. Liu, C.-F. Kang, S.-J. Lin, and J.-H. He, "Surface effect on resistive switching behaviors of ZnO," *Applied Physics Letters*, vol. 99, article 192106, 2011.

- [3] R. Waser, R. Dittmann, C. Staikov, and K. Szot, "Redox-based resistive switching memories nanoionic mechanisms, prospects, and challenges," *Advanced Materials*, vol. 21, no. 25-26, pp. 2632–2663, 2009.

- [4] I. H. Inoue, S. Yasuda, H. Akinaga, and H. Takagi, "Non-polar resistance switching of metal/binary-transition-metal oxides/metal sandwiches: Homogeneous/inhomogeneous transition of current distribution," *Physical Review B*, vol. 77, article 035105, 2008.

- [5] Y. Fujisaki, "Review of Emerging New Solid-State Non-Volatile Memories," *Japanese Journal of Applied Physics*, vol. 52, article 040001, 2013.

- [6] K. L. Pey, R. Thamankar, M. Sen, M. Bosman, N. Raghavan, and K. Shubhakar, "Understanding the switching mechanism in RRAM using in-situ TEM," in *Proceedings of the 21st IEEE Silicon Nanoelectronics Workshop, SNW 2016*, IEEE, Honolulu, Hawaii, USA, June 2016.

- [7] S. Mei, M. Bosman, R. Nagarajan, X. Wu, and K. L. Pey, "Compliance current dominates evolution of NiSi2 defect size in Ni/dielectric/Si RRAM devices," *Microelectronics Reliability*, vol. 61, pp. 71–77, 2016.

- [8] J. Molina-Reyes, H. Uribe-Vargas, R. Torres-Torres, P. Mani-Gonzalez, and A. Herrera-Gomez, "Accurate modeling of gate tunneling currents in Metal-Insulator-Semiconductor capacitors based on ultra-thin atomic-layer deposited Al<sup>2</sup>O<sub>3</sub> and post-metallization annealing," *Thin Solid Films*, vol. 638, pp. 48–56, 2017.

- [9] Y. Liu, T. P. Chen, W. Zhu et al., "Charging effect of Al<sub>2</sub>O<sub>3</sub> thin films containing Al nanocrystals," *Applied Physics Letters*, vol. 93, Article ID 142106, 2008.

- [10] M. N. Bhuyian, R. Sengupta, P. Vurikiti, and D. Misra, "Oxygen vacancy defect engineering using atomic layer deposited

HfAlO," Applied Physics Letters, vol. 108, no. 18, article 183501, 2016.

- [11] D. Zhou, U. Schroeder, J. Xu et al., "Reliability of Al<sub>2</sub>O<sub>3</sub>-doped ZrO<sub>2</sub> high-k dielectrics in three-dimensional stacked metalinsulator-metal capacitors," *Journal of Applied Physics*, vol. 108, no. 12, article 124104, 2010.

- [12] B. H. Lee, "Unified TDDB model for stacked high-k dielectrics," International Conference on IC Design and Technology. pp. 83–87, IEEE. Austin, USA (2009).

- [13] X. Zhong, I. Rungger, P. Zapol, H. Nakamura, Y. Asai, and O. Heinonen, "The effect of a Ta oxygen scavenger layer on HfO<sub>2</sub>-based resistive switching behavior: thermodynamic stability, electronic structure, and low-bias transport," *Physical Chemistry Chemical Physics*, vol. 18, pp. 7502–7510, 2016.

- [14] H. Nakamura and Y. Asai, "Competitive effects of oxygen vacancy formation and interfacial oxidation on an ultra-thin HfO<sub>2</sub>-based resistive switching memory: beyond filament and charge hopping models," *Physical Chemistry Chemical Physics*, vol. 18, pp. 8820–8826, 2016.

- [15] X. Li, C. H. Tung, and K. L. Pey, "The nature of dielectric breakdown," *Applied Physics Letters*, vol. 93, no. 7, article 072903, 2008.

- [16] X. Wu, D. Cha, M. Bosman et al., "Intrinsic nanofilamentation in resistive switching," *Journal of Applied Physics*, vol. 113, no. 11, Article ID 114503, 2013.

- [17] X. Wu, S. Mei, M. Bosman et al., "Evolution of Filament Formation in Ni/HfO<sub>2</sub>/SiO<sub>x</sub>/Si-Based RRAM Devices," *Advances in Electronics*, vol. 1, Article ID 1500130, 2015.

- [18] J. Molina, R. Ortega, W. Calleja, P. Rosales, C. Zuniga, and A. Torres, "MOHOS-type memory performance using HfO<sub>2</sub> nanoparticles as charge trapping layer and low temperature annealing," *Materials Science and Engineering: B-Advanced*, vol. 177, pp. 1501–1508, 2012.

- [19] J. Molina, R. Ortega, W. Calleja, P. Rosales, C. Zuniga, and A. Torres, "HfO<sub>2</sub> nanoparticles embedded within a SOG-based oxide matrix as charge trapping layer for SOHOS-type memory applications," *Journal of Non-Crystalline Solids*, vol. 358, no. 17, pp. 2482–2488, 2012.

- [20] S. K. Nandi, X. Liu, D. K. Venkatachalam, and R. G. Elliman, "Effect of Electrode Roughness on Electroforming in HfO<sub>2</sub> and Defect-Induced Moderation of Electric-Field Enhancement," *Physical Review Applied*, vol. 4, article 064010, 2015.

- [21] J. Ke, T. Wei, D. Tsai, C. Lin, and J. He, "Surface effects of electrode-dependent switching behavior of resistive randomaccess memory," *Applied Physics Letters*, vol. 109, no. 13, article 131603, 2016.

- [22] J. Molina, R. Valderrama, C. Zuniga et al., "Influence of the surface roughness of the bottom electrode on the resistiveswitching characteristics of Al/Al<sub>2</sub>O<sub>3</sub>/Al and Al/Al<sub>2</sub>O<sub>3</sub>/W structures fabricated on glass at 300°c," *Microelectronics Relia*bility, vol. 54, no. 12, pp. 2747–2753, 2014.

- [23] C. A. Volkert and A. M. Minor, "Focused Ion Beam Microscopy and Micromachining," MRS Bulletin, vol. 32, no. 5, pp. 389–399, 2007.

- [24] R. Thamankar, N. Raghavan, J. Molina et al., "Single vacancy defect spectroscopy on HfO<sub>2</sub> using random telegraph noise signals from scanning tunneling microscopy," *Journal of Applied Physics*, vol. 119, no. 8, article 084304, 2016.

- [25] A. Ranjan, N. Raghavan, K. Shubhakar et al., "CAFM based spectroscopy of stress-induced defects in HfO2 with experimental evidence of the clustering model and metastable vacancy

- defect state," in *Proceedings of the 2016 International Reliability Physics Symposium, IRPS 2016*, pp. 7A41–7A47, IEEE, Pasadena, California, USA, April 2016.

- [26] A. Ranjan, N. Raghavan, J. Molina, S. J. O'Shea, K. Shubhakar, and K. L. Pey, "Analysis of quantum conductance, read disturb and switching statistics in HfO<sub>2</sub> RRAM using conductive AFM," *Microelectronics Reliability*, vol. 64, pp. 172–178, 2016.

- [27] S. P. Adhikari, M. P. Sah, H. Kim, and L. O. Chua, "Three fingerprints of memristor," *IEEE Transactions on Circuits and Systems*, vol. 60, no. 11, pp. 3008–3021, 2013.

- [28] D. Biolek, Z. Biolek, V. Biolkova, and Z. Kolka, "Some fingerprints of ideal memristors," in *Proceedings of the 2013 IEEE International Symposium on Circuits and Systems, ISCAS 2013*, pp. 201–204, Beijing, China, May 2013.

- [29] L. Chua, "Resistance switching memories are memristors," *Applied Physics A*, vol. 102, no. 4, pp. 765–783, 2011.

- [30] J. Molina, R. Thamankar, and K. L. Pey, "Performance of ultrathin HfO<sub>2</sub>-based MIM devices after oxygen modulation and post-metallization annealing in N<sub>2</sub>," *Physica Status Solidi (A) Applications and Materials Science*, vol. 213, no. 7, pp. 1807–1813, 2016.

- [31] R. Thamankar, F. M. Puglisi, A. Ranjan et al., "Localized characterization of charge transport and random telegraph noise at the nanoscale in HfO," *Journal of Applied Physics*, vol. 122, no. 2, article 024301, 2017.

Submit your manuscripts at https://www.hindawi.com

Journal of Discrete Mathematics