# Power Solution Guide Management

# Solving Today's Hot Challenge

# INSIDE

# **ARTICLES**

Conquering the Three Challenges of **Power Consumption**

The Virtex-4 Power Play

# WHITE PAPERS

Power vs. Performance: The 90 nm Inflection Point

# **APPLICATION NOTES**

Managing Power with CoolRunner-II CPLDs

# Support Across The Board.

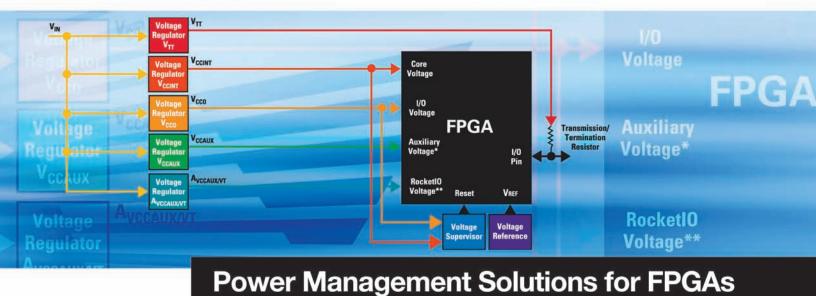

# National Devices supported:

- Voltage Regulators

- Voltage Supervisors

- Voltage References

## Xilinx Devices supported:

- Virtex<sup>TM</sup>

- Virtex-E

- Virtex-II

- Virtex-II Pro

- Virtex-4FX, 4LX, 4SX

- Spartan™-II

- Spartan™-IIE

- Spartan-3, 3E, 3L

Avnet Electronics Marketing has collaborated with National Semiconductor® and Xilinx® to create a design guide that matches National Semiconductor's broad portfolio of power solutions to the latest releases of FPGAs from Xilinx.

Featuring parametric tables, sample designs and step-by-step directions, this guide is your fast, accurate source for choosing the best National Semiconductor Power Supply Solution for your design. It also provides an overview of the available design tools, including application notes, development software and evaluation kits.

Go to em.avnet.com/powermgtguide to request your copy today.

Enabling success from the center of technology™

1 800 332 8638 www.em.avnet.com

# CONTENTS

"FPGAs are being used increasingly in many applications, so reducing power consumption in FPGAs provides huge benefits to the system design."

## **ARTICLES**

| Conquering the Three Challenges of Power Consumption |   |

|------------------------------------------------------|---|

|                                                      |   |

| The Virtex-4 Power Play                              | 8 |

#### WHITE PAPERS

| Power/Performan  | ice Inflection at 90 | Onm Technolog | y Node | 13 |

|------------------|----------------------|---------------|--------|----|

| Static Power and | Temperature          |               |        | 29 |

## APPLICATION NOTES

| Using CoolRunner-II Advanc | ed Features       | 37 |

|----------------------------|-------------------|----|

| Low Power Design with Co   | olRunner-II CPLDs | 47 |

| Using DataGATE in CoolRu   | nner-II CPLDs     | 56 |

| Managing Power with Coo    | Runner-II CPLDs   | 64 |

Learn more about power management solutions from Xilinx at: <a href="https://www.xilinx.com/xcell/power1/">www.xilinx.com/xcell/power1/</a>

# More Power to You

Welcome to the first edition of the Xilinx® *Power Management Solution Guide*. At Xilinx, we have heard a clear message from our customers that power is now a key issue in many system designs. No longer an afterthought, power must now be budgeted and managed just as much as the bill of materials cost or system performance. You have told us that meeting only two of these three key parameters just isn't good enough anymore.

With these thoughts in mind, we have assembled a collection of the most recent – and we hope useful – articles, white papers, and application notes dealing with system power management.

This issue includes several articles and white papers discussing the system power advantages and power management features of the Virtex<sup>TM</sup>-4 FPGA solution. Virtex-4 FPGAs dramatically reduce power consumption compared to other FPGAs in all three key power areas – static power, dynamic power, and in-rush or startup current. They offer as much as 73% lower static power with the industry's first triple-oxide technology; as much as 86% lower dynamic power enabled by embedded IP blocks; and the industry's lowest in-rush current.

These savings are enabled with industry-leading technologies, including the industry-first 90 nm triple-oxide technology, high-performance embedded IP, and power-saving configuration circuitry. In addition to the chip technology itself, Xilinx provides comprehensive tools for power system design, including a Web-based power estimator and the post-implementation XPower tool included as part of the ISE<sup>TM</sup> design tool suite.

This issue also features a collection of application notes detailing some of the innovative power-saving features of the CoolRunner<sup>TM</sup>-II CPLD. Long the industry's benchmark for low-power CPLDs, the CoolRunner-II family offers both power-saving technology and power-management features that make it the best choice for today's low-power, portable systems.

We hope you find this solution guide valuable. It is, however, just a sample of the information available to you about this topic. For access to all of the latest on power management, visit our website at www.xilinx.com/xcell/power1/.

Thank you,

Sandeep Vij Vice President Worldwide Marketing

# Conquering the Three Challenges of Power Consumption Why is power such an issue?

by Steve Sharp

Sr. Manager, Corporate Solutions Marketing

Xilinx, Inc.

steve.sharp@xilinx.com

As chip technology progresses to 90 nm and below, power becomes a burning issue in system design. At this node, leakage plays a more major role in total power; smaller interconnect geometries with new dielectric materials affect dynamic power as well.

According to Jordan Selburn of market research firm iSupply, "Leakage current – essentially insignificant at the 0.35 micron node and earlier – has become a major issue as transistors become increasingly leakier. Studies have shown that at the 90 nm node, leakage power can equal dynamic power consumption and even exceed it at the 65 nm node."

Another factor facing system designers is the tighter power budgets around

which they must design. This is not limited to any single type of system, but does affect most designers. Large systems with many boards or modules, as well as portable and consumer products, all face power budgeting issues.

In large systems, power budgeting is typically done for the total system, as well as distributed power regulation on a perboard or per-module basis. With multiple power supplies now on every board, it is not a simple task to increase the power budget for one board without affecting the entire system's power distribution plan.

In line-powered consumer products, the goal is usually to use the smallest and least-expensive power supply possible to keep costs under control. Exceeding the capabilities of a particular model power supply by only a few percent can necessitate the use of a larger, more expensive supply, and this might be unacceptable in light of total system cost. Designers

would rather design in more features to differentiate the product than to use a larger power supply.

In portable consumer products, the overwhelming goal is to extend battery life for as long as possible. For these products, longer battery life – both in active and standby modes – is a significant competitive advantage.

With all of these challenges, it's no wonder that power issues are sounding the alarm bells for system designers today. iSuppli's Selburn continues, "On the customer side, chip designers can consider architectural approaches such as parallel processing at reduced clock speeds to reduce dynamic power, or gated clocks that essentially turn off entire sections of the chip when they are not needed. Despite these techniques, power consumption remains a serious issue for a large portion of the core silicon market, an issue that is becoming worse, not better, with time."

# **System Design Challenges**

There are three key areas of power usage and control challenging system designers today: static power, dynamic power, and in-rush power. Each presents different issues and requires different methods to calculate and manage power.

Static power is the power consumed by a device when it is in its quiescent condition with no input signals being exercised. It is also referred to as steady-state or standby power. In today's 90 nm technology devices, leakage currents in the transistors are the biggest contributors to static power. This is usually the key parameter of concern to designers of portable equipment because of its effect on battery life, especially for devices that spend large amounts of time in a standby condition waiting for input from the outside world.

Dynamic power is the power consumed during normal operation. It is also referred to as operating power. Dynamic power is dependant on operating signal frequency, interconnect capacitance, and operating voltage. Because the voltage dependency is a square function, the reduction in voltage when moving to 90 nm devices has substantially reduced operating power in many devices. However, for large, high-performance systems with high operating frequencies, dynamic power is still a significant component of total system power.

In-rush power is the power required at device power-up. It is also referred to as power-up or start-up power, or power-on surge power (or current). Some devices require many times more power to begin operation than they do during normal operation, thereby placing demands on system power supplies. In a consumer system with very tightly controlled power supply size and cost, ensuring that in-rush power is not more than normal operating power is a key design goal.

Higher power levels can affect both manufacturers and end-customers alike, in four key areas:

Performance. Higher power levels in a chip can limit device and end-system performance by forcing a lower system clock rate to stay within the system power budget.

- Reliability. As power goes up, so does the threat of brown-out and latch-up from high power-on surge. In addition, higher failures-in-time (FIT) rates will be expected due to higher device operating temperatures.

- Cost. As mentioned previously, higher power equals higher cost in the system because of larger, more expensive power supplies and thermal management components such as fans and head sinks.

- End-customer operating expenses.

Higher power also impacts end users in the form of higher power bills (which can be significant for large systems) and shorter battery life for portable products.

This is enabled with industry-leading technologies such as 90 nm triple-oxide technology, high-performance embedded IP, and power-saving configuration circuitry.

Xilinx also provides comprehensive tools for power system design: Virtex-4 datasheet and user guide; a web-based power estimator; and XPower, included in ISE<sup>TM</sup> software.

Virtex-4 devices handle the three types of power usage and control in the following ways:

• Static power. As process geometries shrink to 90 nm and lower, the industry expects higher leakage and higher static power when channel length decreases. Working with fab partner United Microelectronics

Higher power levels in a chip can limit device and end-system performance by forcing a lower system clock rate to stay within the system power budget.

# How Xilinx Helps Manage System Power Virtex-4 FPGAs

With a significant reduction in power consumption over that of the competition, the new Virtex<sup>TM</sup>-4 platform FPGAs offer significant benefits for system design, including reduced thermal concerns, easier power-supply design, lower cost power supply, and higher system reliability. Virtex-4 FPGAs dramatically reduce power consumption when compared to other FPGAs in all three key power areas:

- As much as 73 percent lower static power with the industry's first tripleoxide technology

- As much as 86 percent lower dynamic power enabled by embedded IP blocks

- Negligible in-rush current with unique power-saving configuration circuitry

Corp., Xilinx solved this problem by using triple-oxide technology in the Virtex-4 90 nm process, which reduces leakage current significantly. Two-oxide thicknesses are widely used in the industry today, with a thin oxide in the core and thicker oxide in the I/O area. Virtex-4 devices add a third medium-thick oxide transistor used for certain functions in the FPGA. The result is 50% lower static power than that of Virtex-II Pro FPGAs. Other FPGA vendors have gone the other way when migrating to a 90 nm process, with static power increasing more than 2X compared to 130 nm devices.

Dynamic power. New and existing Virtex-4 embedded functions lower dynamic power by 5 to 20x compared

to Virtex-II Pro FPGAs. This results in as much as 86% lower dynamic power than that of other 90 nm FPGAs.

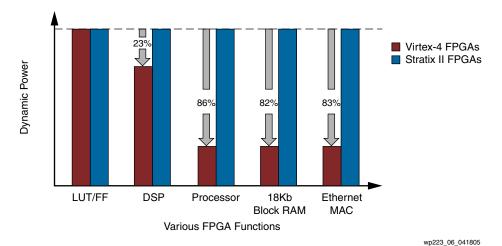

Note these specific examples:

- PowerPC<sup>TM</sup> as much as 86% power reduction

- Block RAM as much as 82% power reduction

- DSP as much as 23% reduction with XtremeDSP<sup>TM</sup> slice

- Ethernet MAC as much as 83% power reduction

- Logic although Virtex-4 devices consume similar dynamic power-perlogic cell when compared to other FPGAs, the embedded IP blocks often allow fewer general-purpose logic cells to be used. For example, when building a source-synchronous I/O (SSIO) interface, the new ChipSync<sup>TM</sup> block reduces the number of logic cells used.

- In-rush power. Other high-performance 90 nm FPGAs have exhibited levels of in-rush power more than four times that of Virtex-4 FPGAs. In Virtex-4 devices, by spending considerable time designing very power-efficient configuration logic, Xilinx has been able to keep in-rush power within 15-20% of the static power requirements and below typical operating power. This removes the need to use a larger power supply just to address in-rush current.

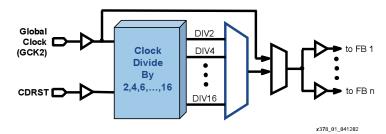

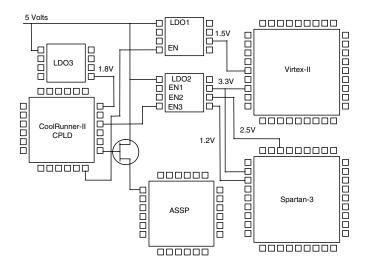

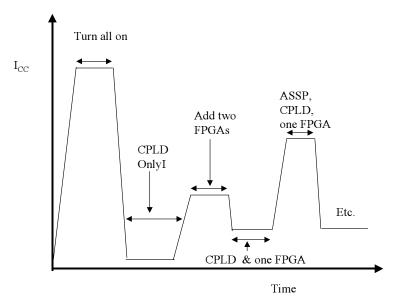

#### CoolRunner-II CPLDs

When Xilinx designed the CoolRunner<sup>TM</sup>-II family of low-power CPLDs, our goal was to deliver one of the industry's lowest power levels for a programmable logic device. These devices have standby current requirements of less than 20  $\mu$ A, making them ideal for battery-powered portable devices. Other CPLDs claiming to be low power have standby power 100 to 1000x higher, affecting battery life so significantly that they are unsuitable for portable applications.

The static RealDigital technology used in the logic of CoolRunner-II devices does away with power-hungry sense amplifiers and delivers low dynamic power as good as any other device available today.

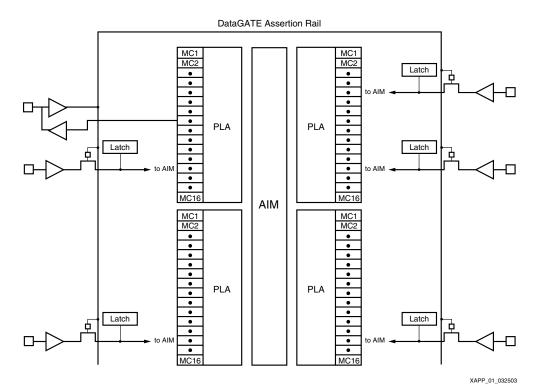

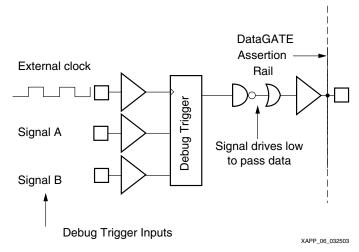

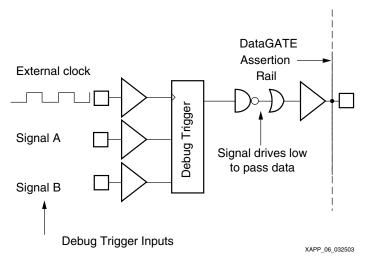

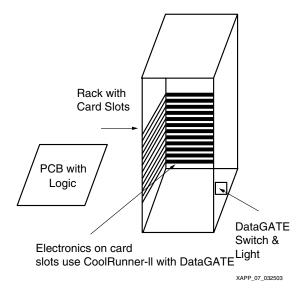

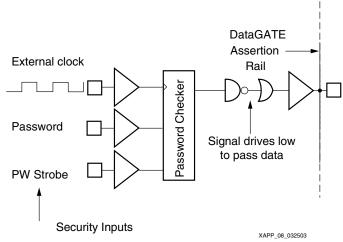

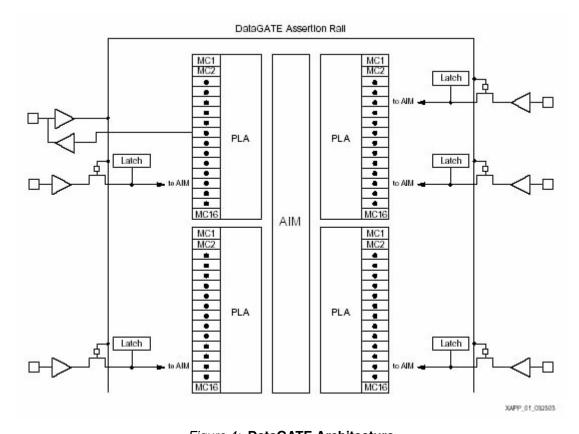

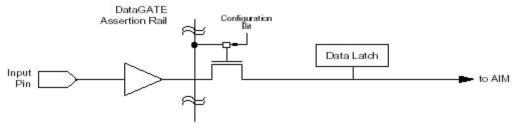

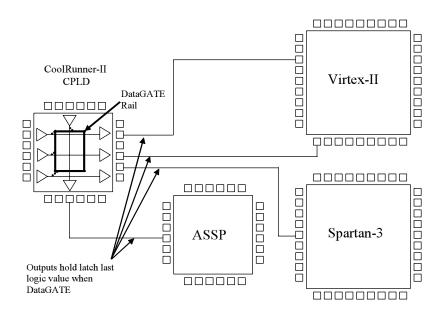

In addition to these advantages in the basic circuit design and process technology, CoolRunner-II devices also offer power-management features unique to the CPLD industry, including a DataGate feature to reduce effective logic usage in the device and clock management and input hysteresis features to reduce internal operating frequencies and dynamic power.

# Spartan-3 FPGAs

Our customers have told us that in today's cost-conscious consumer products, being forced to put in a bigger supply just to supply a high power-on or in-rush current is not a viable option for their system designs.

Attention to detail when designing the Spartan-3 configuration logic has yielded devices where the maximum quiescent power alone is guaranteed to be sufficient to power up the device. Spartan-3 devices have no in-rush current or power specification. When using these low-cost devices, you can focus on the product features and design without worrying about increased system cost because of high in-rush power requirements.

# **Power Management Tools**

Web Power Tools are pre-implementation tools that estimate a design's power consumption based on the expected utilization of device resources, operating frequencies, and toggle rates.

Once you have implemented your design in the Xilinx software tools, you can use XPower to accurately estimate the power consumption. Actual power consumption must be determined in-circuit under the appropriate operating conditions.

# Web Power Tools

The intuitive interface guides you through the steps of the data-entry process and ensures the most accurate estimates possible. The equations and values used by Web Power Tools are based on device characterizations for the family. Web Power Tools are available for the Virtex-4, Virtex-II Pro, Virtex-II, Virtex/Virtex-E, and Spartan-3 FPGA families, as well as CoolRunner-II CPLDs.

#### XPower

XPower is the first power-analysis software available for programmable logic design, allowing the analysis of total device power, power-per-net, routed, partially routed, or un-routed designs.

#### Power Management Hardware

Tools for managing power are not just of the software variety. Power-management chips from National Semiconductor, Intersil, Texas Instruments, and Linear Technology are available to make the job of supplying the multiple supply voltages needed by today's FPGAs easier, and they can be valuable companions to Virtex-4 or Spartan-3 devices. Their individual capabilities are highlighted in this issue of the *Xcell Journal* in the following pages.

#### Conclusion

To conquer the key challenges of power consumption, it takes a combination of good product design, proper device technology, and tools that let you take control of system power management.

Xilinx is an industry leader in power management and now offers many advantages within its programmable solutions:

- Virtex-4 FPGAs consume 1 to 5W less power than competing 90 nm FPGAs.

- Spartan-3 FPGAs are the one of the only low-cost FPGAs in the industry to eliminate power-on surge. In these devices, the maximum quiescient power alone is sufficient to guarantee device power-up.

- CoolRunner-II CPLDs are the world's lowest power CPLDs, ideal for even the most power-critical portable applications.

- Xilinx offers a comprehensive suite of power management tools, from Web Power Tools to the XPower analysis tool integrated into the ISE environment.

You can find comprehensive information on power consumption and solving key power challenges with Xilinx devices, tools, and solutions at www.xilinx.com/power/.

# The Virtex-4 Power Play

The latest Xilinx FPGA offers revolutionary power innovations.

by Matt Klein

Sr. Staff Engineer, Applications Engineering,

Advanced Products Division

Xilinx, Inc.

matt.klein@xilinx.com

Device power consumption is a primary issue in the semiconductor industry – as process technologies get smaller and faster, they normally consume more power, putting power concerns and performance at odds. The new Virtex-4<sup>TM</sup> FPGA family from Xilinx® employs innovative architectural features and clever IC design techniques that dramatically reduce power consumption, without compromising performance. This bucks expected trends nor-

mally associated with the reduced feature sizes of 90 nm process technology.

In this article, we'll explore how Xilinx IC designers achieved remarkable power efficiency in the high-performance Virtex-4 FPGA.

# **Components of Power Consumption**

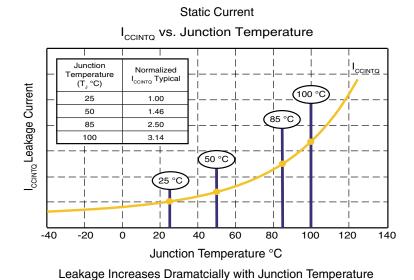

There are two main components to power consumption: static and dynamic. Static or quiescent power is mainly dominated by transistor leakage current. When this current is listed in data sheets, it is listed as I<sub>CCINTQ</sub> and is the current drawn through the V<sub>CCINT</sub> supply powering the FPGA core.

Dynamic or active power has components from both the switching power of the core of the FPGA and the I/O being switched. The

dynamic power consumption is determined by the node capacitance, supply voltage, and switching frequency and governed by the basic formula  $P=CV^2f$ .

Both static and dynamic power have been significantly reduced in Virtex-4 devices, even when compared to Virtex-II Pro<sup>TM</sup> devices.

## **Dramatic Power Reduction**

The Virtex-4 product family has reduced power consumption in several key areas. The power-per-CLB has been cut in half, with static power reduced by 40% and dynamic power reduced by 50% when compared to the 130 nm Virtex-II Pro FPGA and other 90 nm FPGAs. Furthermore, certain hard-logic silicon functions in the Virtex-4 FPGA reduce power consumption by 80-95%, a whopping factor when compared to the same functions implemented in configurable logic blocks and programmable interconnect routing.

Additionally, comprehensive power planning tools are available to help you get an idea, up front, of power consumption for your Xilinx FPGA under its operating conditions.

# Reduced Power Consumption Benefits

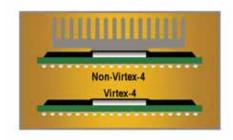

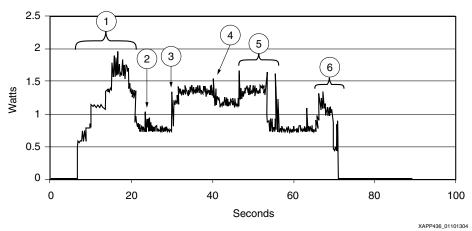

Reduced power consumption benefits cut across a few areas of product design in reduced thermal concerns as well as eased power supply design (see Figure 1).

- Reduced thermal concerns When you reduce power consumption in a device or system, you use smaller heat sinks, or no heat sinks at all in some cases. You also have simpler thermal system design from the point of view of reducing airflows and fan size needs.

- Easier power supply design You can also use smaller supply circuitry and reduce the number of components in the power supply. Using less PCB space allows you to reduce the cost of the power system. Plus, by not having your device consume as much power, you can achieve higher reliability by lowering the temperature of the FPGA die.

Figure 1 – Virtex-4 devices reduce thermal concerns and simplify power supply design.

# Static Power Trends in 90 nm Technology

The reduction in transistor size in 90 nm technology has several effects on power consumption. The biggest potential problem is in the area of static power.

# Scaling Trends for Static Power

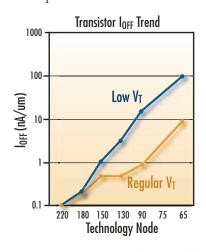

As we mentioned earlier, static power is dominated by transistor leakage current. Unfortunately, channel leakage increases as transistor size decreases. This is especially true for low  $V_{\rm T}$  transistors where  $V_{\rm T}$  refers to voltage threshold between the gate and drain.

Low  $V_T$  transistors are the fastest transistors – the ones with the shortest turn-on and propagation delay – that IC designers use inside the FPGA when the highest speed performance is needed. Regular  $V_T$  transistors are also used when less performance is acceptable, but this only helps so much with leakage.

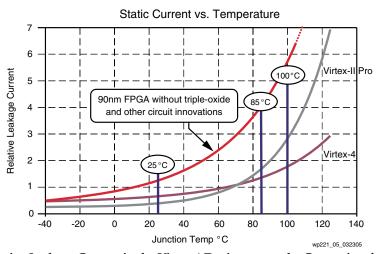

Figure 2 shows that leakage goes up dramatically when moving from 130 nm to 90 nm technology. The Virtex-II Pro device uses 130 nm process technology, whereas the new Virtex-4 device uses 90 nm process technology.

# Triple-Oxide — The Savior of Static Power

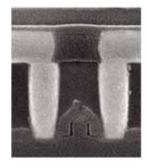

Triple-oxide simply means that we use a third thickness of oxide in making some of the transistors in the FPGA (two oxide thicknesses are used in devices like the Virtex-II Pro FPGA). Most transistors in the past had a thin oxide layer. Within those transistors could be low V<sub>T</sub>, regular V<sub>T</sub>, NMOS, or PMOS transistors. Thick-oxide transistors are mostly used for I/O drivers and a few other functions.

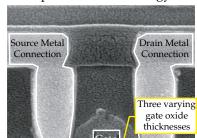

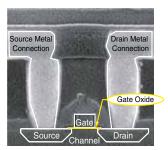

Oxide deposition thickness is a very stable and controllable process in the semiconductor industry because it depends on temperature, concentration, and exposure time. Figures 3a and 3b show the Virtex-4 transistor with the middle oxide thickness used in the triple-oxide process. You may notice that the oxide thickness is still very, very thin, but this thicker oxide transistor has much lower leakage than the standard thin-oxide low V<sub>T</sub> and regular V<sub>T</sub> transistors used in Virtex-II Pro FPGAs and in various parts of Virtex-4 FPGAs.

Figure 2 – Transistor leakage trends due to process scaling

Why Doesn't Everyone Use Triple-Oxide? If triple-oxide is such a great process, why don't other companies like Intel<sup>TM</sup> or IBM<sup>TM</sup> use it in their own ASICs?

They probably would if it benefited them. The reason they don't is that all of their transistors need to run at speed; hence, they must use the low V<sub>T</sub> leakier transistors for everything. FPGAs can have many different transistor types, which can be selected for function, power, or performance.

FPGAs can use different transistor types for different functions, and Xilinx designers have accomplished this balance.

# Optimizing Performance and Leakage

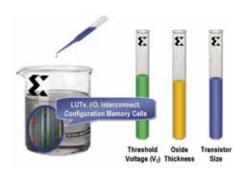

Our IC designers have many things that they can do to adjust the mix to optimize for certain factors. The Virtex-4 FPGA is the first Platform FPGA designed for high speed and low power.

Low  $V_T$  transistors are used only where necessary for maximum speed, while the middle thickness of oxide from the triple-oxide process may be used for less aggressive performance with very low leakage. You may use different sizes and types of transistors for performance and function. Combinations are also possible, such as small and medium-sized low  $V_T$  fast transistors and small and medium-sized middle oxide thickness transistors. It is not a one-size-fits-all procedure.

Xilinx IC designers were given a directive to reduce power, among other things, in the Virtex-4 platform while maintaining the highest system performance. These transistors are used across the various FPGA functions of LUTs, I/O, interconnect, and configuration memory cells. Even within a given FPGA function, all transistors don't need to be the same, and that is up to the Xilinx IC designers (see Figure 4).

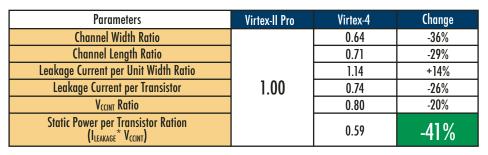

The surprising result of this balancing is that the overall static current in Virtex-4 devices with 90 nm process is reduced by 40% when compared to Virtex-II Pro devices with 130 nm process. Table 1 shows a chart of the weighted average changes to the transistors in the Virtex-4 die compared to Virtex-II Pro die, which allows you to arrive at the reduced transistor leakage in the Virtex-4 FPGA.

Figure 3a, 3b – Middle oxide thickness Virtex-4 transistor used in triple-oxide process and with highlighted portions of the transistors

Figure 4 – Optimal transistor mix for minimizing leakage and maximizing performance

# **Dynamic Power Reduction**

Static power reduction, while dramatic, is not the only power winner that you can take advantage of. Dynamic power is also reduced by 50% when compared to Virtex-II Pro FPGAs.

The dynamic power in the FPGA is governed by the following equation:

$P_{Dynamic} = FPGA_{Core}(CV^2f) + FPGA_{I/O}(CV^2f)$

The Virtex-4 family of FPGAs has the following:

- Reduced FPGA core dynamic power

- Internal operating voltage is the dominant factor

- Secondary scaling by frequency (f) and node capacitance (C)

- Constant FPGA I/O dynamic power

- Unchanged voltage swing (V<sub>I/O</sub>), toggle rate (f), and pin/pad capacitance (C) for a given I/O standard

So you can see that we may be able to have an effect on dynamic power inside the device, but that dynamic power consumed by I/O switching remains unchanged.

When we go from the 130 nm process of the Virtex-II Pro FPGA to the 90 nm process of the Virtex-4 FPGA, the internal supply voltage changes from 1.5V to 1.2V. This reduces the dynamic power consumption for every internal transistor by 36%  $(1-\frac{[1.2]}{[1.5]})^2$  of that in the Virtex-II Pro FPGA.

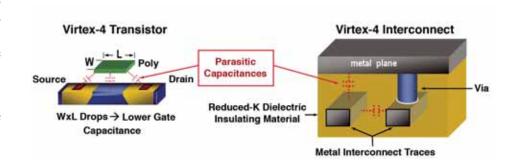

Additionally, the FPGA internal composite capacitance is reduced in the Virtex-4 FPGA. This internal capacitance comprises transistor parasitic capacitances and trace-to-metal and trace-to-trace capacitances for the interconnecting metal traces. Figure 5 shows the capacitance involved relative to their structures.

As mentioned earlier, dynamic power is related to the bulk capacitance and internal voltage levels being switched,  $P=CV^2f$ . All things being equal, having a lower internal capacitance for the interconnects would be a benefit for dynamic power and reduced resistor-capacitor delay, but other factors contribute to interconnect capacitance, such as distance above the metal plane, interconnect width, and interconnect length.

Additionally, other parasitic capacitances such as gate-to-drain and gate-to-source are also part of the equation. Total capacitance for a path is based on a complex combination of parasitic capacitance

Figure 5 – Internal FPGA capacitance comprises parasitic transistor and interconnect capacitances

Does low-K reduce power? Low-K refers to the dielectric insulating material between the metal traces in the FPGA. Lower K dielectric insulating layers do reduce internal capacitances per unit trace length, but "low-K" is a relative term. Xilinx has reduced-K-insulating materials, and in the past has used low-K itself; we may do so again in the future.

in the transistors; the architecture of the interconnect paths and actual path lengths; and the number of hops through interconnect switches. Xilinx has reduced the overall capacitance for those components in the Virtex-4 FPGA.

The overall effect is mostly due to reduced gate capacitance and lowers capacitance by 20% for Virtex-4 FPGAs when compared to Virtex-II Pro FPGAs. Table 2 shows a dynamic power reduction of 50% for the Virtex-4 FPGA when compared to the Virtex-II Pro FPGA. We have a 23% reduction in dynamic power when running at a 50% higher frequency.

Because the Virtex-4 FPGA is a much higher performance device than the Virtex-II Pro FPGA, you may need to operate it at higher clock speeds to meet newer demanding performance targets that could never be achieved in previous systems.

Table 1 – Overall weighted average transistor leakage and parameter comparisons for 90 nm Virtex-4 transistors relative to 130 nm Virtex-II Pro transistors

| Parameters                | Virtex-II Pro | Virtex-4 | Change |

|---------------------------|---------------|----------|--------|

| V <sub>CCINT</sub>        | 1.5           | 1.2      | -20%   |

| C <sub>total</sub> (rel.) | 1.0           | 0.8      | -20%   |

| f <sub>MAX</sub> (rel.)   | 1.0           | 1.5      | +50%   |

| Power at Same Frequency   | 2.25          | 1.15     | -49%   |

| Power at f <sub>MAX</sub> | 2.25          | 1.73     | -23%   |

Table 2 – Chart showing changes in internal FPGA in Virtex-4 devices compared to Virtex-II Pro devices and the effect on dynamic power

| Parameters            | Virtex-II Pro | Virtex-4    | Logic Slice<br>Reduction | Logic Slice<br>Power Reduction |

|-----------------------|---------------|-------------|--------------------------|--------------------------------|

| QDR II SRAM Interface | 550 slices    | 125 slices  | 77%                      | 89%                            |

| SPI-4.2 Core          | 5000 slices   | 3900 slices | 22%                      | 61%                            |

Logic slice power reduction =

$$100^* \left(1 - 0.5 \frac{\text{Virtex-4 slice count}}{\text{Virtex-II Pro slice count}}\right)\%$$

Note: The factor of 0.5 above comes from the fact that Virtex-4 power per slice is 1/2 of the Virtex-II Pro power per slice because of the 50% dynamic power reduction in Virtex-4 devices compared to Virtex-II Pro devices.

Table 3 – QDR II SDRAM and SPI-4.2 core benefit in reduced power consumption from significant logic cell reduction due to new Virtex-4 ChipSync block

## **Embedded Blocks**

Another major area of improvement in power consumption is in the area of embedded functions. This has always been a strength in Xilinx FPGAs, but it is more so in the Virtex-4 FPGA, even when compared to the feature-rich Virtex-II Pro FPGA.

In Virtex-4 FPGAs you can take further advantage of both static and dynamic power reduction by using the embedded functions, which are built as hard-logic functions.

When embedded functions are implemented as hard-logic functions instead of in configurable logic blocks and programmable interconnects, there is a lot less static and dynamic power consumed. This is because far fewer transistors are used for hard, fixed logic than for programmable logic. Additionally, there are no transistors needed to make connections for interconnects in the embedded functions, because there are no programmable interconnects.

Xilinx has carefully studied some of the functions that engineers like you have struggled with and that we have also found tedious to implement within the FPGA programmable logic. The new embedded functions lower power by 80-95% compared to their configurable logic blocks and routed counterparts in programmable silicon.

# **Comprehensive Power Planning Tools**

Another useful thing in planning power is that Xilinx data sheets show you both typical and maximum power consumption numbers. Maximum numbers are for worst-case process, temperature, and voltage, but many designers are very happy to work with typical numbers, depending on their application and the number of parts being used in one system.

One additional very useful thing that you can take advantage of in planning for power consumption in Xilinx FPGAs are power planning tools. Xilinx web power tools are available for estimating power early in the design cycle. Also, as part of the Xilinx design flow, XPower looks in more detail at a mapped or routed design. Both can be found, along with power application notes, by searching the Xilinx website for the phrase "Xilinx Power Tools."

#### **Conclusion**

Xilinx has made profound improvements in both static and dynamic power in the Virtex-4 90 nm family of FPGAs when compared to Virtex-II Pro FPGAs – and (we believe) in comparison to our competitors. We have done this through a multi-pronged, purposeful approach in the areas of reduced leakage current, reduced dynamic power consumption, and embedded functions, without compromising performance. These, along with comprehensive power planning tools, make the Virtex-4 device an excellent choice for a high-performance FPGA system.

For more information about power consumption in Virtex-4 and other Xilinx FPGAs, visit <a href="https://www.xilinx.com/products/design\_resources/design\_tool/grouping/power\_tools.htm">www.xilinx.com/products/design\_resources/design\_tool/grouping/power\_tools.htm</a>.

# Virtex-4 Embedded Functions and Reduction of Dynamic Power

- PowerPC 50% power reduction compared to Virtex-II Pro PowerPC

- 10:1 power reduction over FPGA fabric-built version

- DSP XtremeDSP<sup>TM</sup> slice greatly reduces logic cells, which previously needed many filtering functions

- 20:1 power reduction over Virtex-II Pro separated multiply/accumulate functions

- SSIO New ChipSync<sup>TM</sup> block reduces logic cell count for SSIO (source synchronous I/O) designs

- Significant logic cell savings for various memory and networking interface designs leads to reduction in overall power up to 9:1 for selected designs (see Table 3)

- Embedded Ethernet MAC(s) No need to use logic and interconnect for MAC function, which saves

>3,000 logic cells for the Xilinx implementation

- FIFO SmartRAM<sup>TM</sup> memory includes built-in FIFO controllers, which can save hundreds of logic cells per FIFO and greatly simplify design as well

11

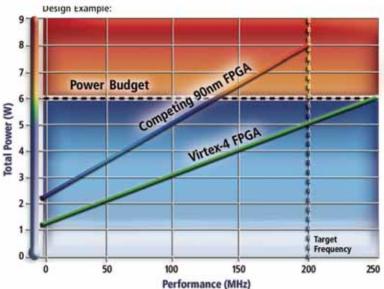

Design Example: LX60 vs. 2S60. Target Frequency = 200 MHz, Worst-case process. 20K LUTs, 20K Flip-Flops, 1Mbit On-Chip RAM, 64 DSP Blocks, 128 2.5V I/Os Based on Xilinx tool v4.0 and competitor tool v2.1 For higher density devices, achieve up to 5W lower power

Get 1-5W lower power per FPGA, only with the Virtex-4 family

Check the specs for yourself at realistic operating temperatures  $(T_j = 85^{\circ}C)$ . Different logic architecture or dielectric just won't do it. No competing FPGA comes close to Virtex-4 for total power savings—take it to the lab and see.

- · 73% lower static power

- · Up to 86% lower dynamic power

# UNIQUE TRIPLE-DXIDE TECHNOLOGY & EMBEDDED IP

At the 90nm technology node, power is the next big challenge for system level designers. An inferior device can suffer leakage, dramatic surges in static power, and thermal runaway. That's why we designed our Virtex-4 FPGAs with Triple-Oxide Technology\*, embedded IP, and power-saving configuration circuitry. Now you can meet your performance goals, while staying within the power budget.

Visit www.xilinx.com/virtex4/lowpower today, and get the right solution on board before your power issues start heating up.

www.xilinx.com/virtex4/lowpower

Seminar Today

BREAKTHROUGH PERFORMANCE AT THE LOWEST COST

White Paper: Virtex-4 Family

# Power vs. Performance: The 90 nm Inflection Point

By: Anil Telikepalli

The debate over which high-performance 90 nm FPGA has the lowest power is "heating up," and for good reason. The industry has crossed a critical inflection point at 90 nm, where performance competes with power and thermal budgets. Customers want as much performance as possible; increasingly, however, the decision about which FPGA to use is based on which device consumes the least amount of power. This white paper discusses performance versus power consumption in 90 nm FPGAs and how the Virtex<sup>TM</sup>-4 family provides the best of both worlds: high performance and low power consumption.

# Introduction

Excessive power is expensive in many ways. It creates the need for special design and operational considerations – requiring everything from heat sinks to fans to sophisticated heat exchangers. Even the cost of building larger power supplies must be taken into consideration. Overall, increased power requires more of everything, including: more area on the PCB, a larger chassis, more floor space, and larger air conditioning systems. The costs continue to compound.

Perhaps the most critical issue is the effect excessive power can have on reliability. As the junction temperatures rise, transistors consume more power, thereby further increasing the temperature of the device. Continuously operating systems with junction temperatures running from 85°C to over 100°C increases reliability issues.

Fortunately, Xilinx encountered the first evidence of this 90 nm inflection point in the early development stages of Spartan<sup>TM</sup>-3 FPGAs, the first Xilinx FPGA family for the 90 nm process. Xilinx began immediately developing new ways to cope with the inherent power issues posed by the 90 nm process. Consequently, when the higher-performance Virtex-4 family was introduced in September 2004, Xilinx was confident that the new family would simultaneously deliver the best of both worlds – the highest performance and lowest power consumption in a 90 nm FPGA.

# Reducing Power in FPGAs

14

# The Triple Challenge

There are two major components to power consumption in FPGAs: static power, and dynamic power. Inrush current is another factor that can occur when the FPGA is powered on. Each component poses a unique challenge. For the 90 nm FPGA, the most challenging component is static power.

# **Static Power**

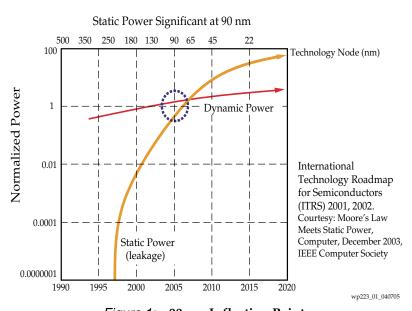

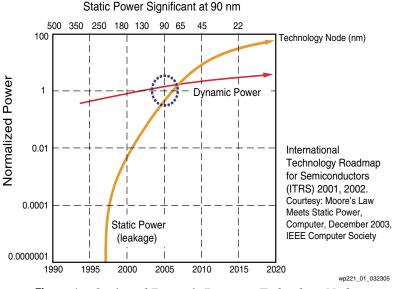

Static power consumption occurs as a result of leakage current in the transistors that comprise the FPGA. As transistors get smaller (with each new process), their leakage current increases. This principle is one of the major reasons the 90 nm process crosses a major inflection point (Figure 1).

Figure 1: 90 nm Inflection Point

For the first time, static power is threatening to eclipse dynamic power as the component responsible for the greatest amount of total power consumption in an FPGA. This is partly due to the fact that as processes get smaller, the core voltage decreases; consequently, the rate of increase in dynamic power drops, despite the increase in frequency that regularly accompanies a new process. In contrast, below 0.25 microns static power has grown exponentially with each new process.

This is where the inflection point really becomes a critical factor for the FPGAs and where Xilinx has established a substantial lead. Smaller transistors are faster, but they leak more. However, unlike ASICs, ASSPs, and microprocessors, Xilinx FPGAs do not need all of their transistors to switch at maximum speed. A substantial number of transistors comprise the configuration memory cells used to select logic and routing, and pass transistors used to implement the programmable interconnect routing. Configuration memory cells do not need to be fast, and programmable interconnect transistors only need to be fast from source to drain and not under gate control. These factors allow leakage to be reduced without compromising performance.

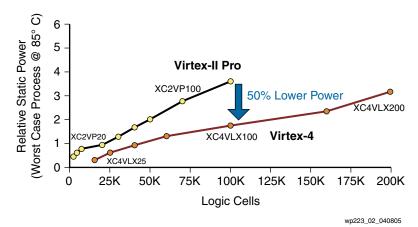

Virtex-4 FPGAs take advantage of the abundance of these particular types of transistors to incorporate a new process approach called "triple-oxide technology" to solve the static power problem. Figure 2 shows how Virtex-4 FPGAs consume 50% lower static power than its predecessor, the 130 nm Virtex-II Pro FPGAs.

Figure 2: The use of "triple oxide" technology reverses the trend: the Virtex-4 device actually consumes less static power than its 130-nm predecessor.

# What is Triple-Oxide Technology?

For many years, Xilinx and other semiconductor vendors have used two gate-oxide thicknesses: a standard thin layer used for the vast majority of transistors and a thick oxide layer for I/O drivers. With the introduction of Virtex-4 FPGAs, Xilinx has utilized *triple-oxide*, which refers to a third thickness of gate oxide used in making the configuration memory cells and pass transistors.

Oxide deposition thickness is a very stable and controllable process in the semiconductor industry. Semiconductor manufacturers can accurately set oxide thickness by choosing temperature, concentration, and exposure time. Figure 3 shows the Virtex-4 transistor with the middle oxide thickness used in the triple-oxide process. Although this third oxide layer is still very thin, these transistors exhibit substantially lower leakage than the standard thin-oxide low  $V_T$  and regular  $V_T$  transistors used in Virtex-II Pro FPGAs and in various other parts of Virtex-4 FPGAs.

# Triple-Oxide Technology

Figure 3: Virtex-4 Transistor Middle Oxide Thickness

wp223\_03\_040705

In addition to using triple-oxide, Xilinx optimized a number of other transistor parameters to balance performance and leakage across I/O, configuration memory, interconnect pass transistors, as well as logic and interconnect buffers (Table 1).

Source

Table 1: Triple-Oxide Technology and Other Transistor Parameters Used for Power Optimization

| Function                             | Oxide Thickness | Voltage Threshold<br>(V <sub>T</sub> ) | Channel Length | Speed                | Leakage     |

|--------------------------------------|-----------------|----------------------------------------|----------------|----------------------|-------------|

| I/O                                  | Thick           | High                                   | Longest        | Fast                 | Lowest      |

| Config Memory                        | Medium          | Medium                                 | Long           | Slow                 | Low         |

| Interconnect Pass<br>Gates           | Medium          | Low/Medium                             | Short          | Fast<br>Source→Drain | Low         |

| Logic and<br>Interconnect<br>Buffers | Thin            | Low                                    | Short          | Very Fast            | Medium/High |

The use of triple-oxide technology in Virtex-4 devices dramatically reduced the static power component for the entire family.

Other optimizations were made to reduce leakage and hence, static power. These include enhancements to gate length,  $V_T$  and oxide thickness. The combination of these effects on leakage and performance is shown in Figure 1.

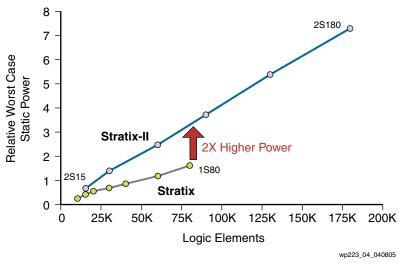

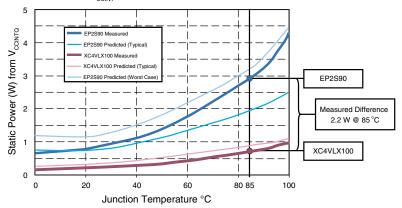

As mentioned earlier, a comparison of relatively equivalent devices from both the 130 nm Virtex-II Pro family and the 90 nm Virtex-4 family reveals 50% less static power consumed by the Virtex-4 device (Figure 2). This is the first time in FPGA history that static power decreased when moving to a new smaller process. In contrast, Stratix II FPGAs consume two times more power than previous 130 nm Stratix FPGAs (Figure 4).

Figure 4: Stratix-II Exhibits a Typical Increase in Worst-case Static Power Consumption Expected in Transitioning to the 90 nm Process – Without Triple-Oxide!

# **Dynamic Power**

The three contributing elements to dynamic power in the FPGA core are voltage, frequency, and parasitic capacitance. Fortunately, as previously mentioned, the core voltage and capacitance decrease with each new smaller process, which lowers dynamic power. If designs require higher operating frequencies, dynamic power increases. The well-known formula for dynamic power that applies here is:

$$P = CV^2f$$

Equation 1

In addition, dynamic power is proportional to the data toggle rate.

One major area of improvement in power consumption is in the area of embedded functions. This has always been a strength in Xilinx FPGAs, but it is more so in the Virtex-4 FPGA, even when compared to the feature-rich Virtex-II Pro FPGA.

When embedded functions are implemented as hard-logic functions instead of configurable logic blocks and programmable interconnects, less static and dynamic power are consumed. This is because far fewer transistors are used for hard, fixed logic rather than programmable logic. Additionally, transistors are not needed for interconnects in the embedded functions, because there are no programmable interconnects.

These hard IP cores occupy far less real estate, deliver much higher performance, and consume 80-95% less power than soft IP versions of the same functions. In addition, by making these hard IP cores programmable and parameterizable, Xilinx provides designers with the flexibility they have come to expect from an FPGA. No other FPGA vendor provides so many hard IP cores for common functions.

Functions that Xilinx provides as hard IP cores in Virtex-4 FPGAs include:

- 450 MHz PowerPC<sup>TM</sup> processors for all microcontroller and embedded processing applications with an APU interface for hardware acceleration. A soft implementation would invariably consume several thousand look-up tables (LUTS) and flip-flops (FFs). Virtex-4 PowerPC processors also contain their own dedicated 16 Kbyte instruction and 16 Kbyte data cache. In addition to providing much better performance, these optimized cache memories consume much less power than building the equivalent-sized cache out of internal FPGA block memory.

- 500 MHz XtremeDSP<sup>TM</sup> slice for simple math and filters to complex highperformance DSP functions. With 40 op-modes and the ability to cascade multiple

- slices without extra logic, each DSP slice functionality implemented as a soft core would cost anywhere from tens to hundreds of LUTs and FFs.

- 500 MHz Digital Clock Managers (DCM) and Phase Matched Clock Dividers (PMCD) that support clock synthesis, clock management, and phase matching. Unlike embedded PLLs, DCMs and PMCDs do not require special supply rails.

- ChipSync™ block in every I/O with built-in SERDES and data-alignment function to simplify source-synchronous interfaces in memory, networking, and telecom applications. Implemented as soft IP, each ChipSync block control circuitry would consume tens to hundreds of LUTs and FFs.

- 622 Mb/s 10.3125 Gb/s RocketIO™ transceivers with built-in Physical Coding Sublayer (PCS) and Physical Media Attachment (PMA). With support for 8B/10B, 64B/66B, custom coding, elastic buffers, clock-data recovery, and multiple equalization options, implementing this functionality in soft IP would cost thousands of LUTs and FFs per transceiver. An external SERDES typically consumes much more power because the FPGA to external SERDES is typically high-performance parallel I/O. These parallel I/O can burn far more power than the Serial I/O channels.

- Tri-mode Ethernet MACs that run at 10/100/1000 Mb/s and can interface directly with RocketIO transceivers. Here again, a soft IP implementation would consume a few thousand LUTs and FFs.

- Smart RAM memory with distributed RAM and block RAM. Each LUT has builtin circuits to turn it into a distributed RAM/ROM, as well as a 16-bit shift-register.

Each block RAM has built-in ECC for error correction and built-in control circuits

to implement an asynchronous FIFO. All this functionality implemented in soft IP

would consume hundreds of LUTs and FFs per block RAM.

Besides the obvious advantages associated with moving these commonly used blocks into hard IP, one must not overlook the inherent contribution the Xilinx Advanced Silicon Modular Block (ASMBL) architecture makes to the Virtex-4 dynamic power advantage. Because each of the three families – the LX, FX, and SX – is meant to satisfy distinct requirements for a particular application domain (logic, embedded processing, and signal processing), their standard ratio of logic cells, memory, I/O, DSP, processors, etc., has been optimized for that domain. Consequently, the Virtex-4 device is the first FPGA to offer domain-optimized dynamic power consumption (Table 2).

| Table 2: The Virtex-4 Domain-optimized Functions that Substantially | Improve Dynamic Power Efficiency |

|---------------------------------------------------------------------|----------------------------------|

|---------------------------------------------------------------------|----------------------------------|

| Functions             | Virtex-4 LX | Virtex-4 SX   | Virtex-4 FX            |

|-----------------------|-------------|---------------|------------------------|

| Logic Cells           | 14 to 200K  | 23 to 55K     | 12 to 140K             |

| Embedded Memory       | 0.9 to 6 Mb | 2.3 to 5.7 Mb | 0.6 to 10 Mb           |

| DCMs                  | 4 to 12     | 4 to 8        | 4 to 20                |

| XtremeDSP Slices      | 32 to 96    | 125 to 512    | 32 to 192              |

| SelectIO Signalling   | 240 to 960  | 320 to 640    | 240 to 896             |

| RocketIO Transceivers | N/A         | N/A           | 0 to 24 channels       |

| PowerPC Processors    | N/A         | N/A           | 1 or 2 processors      |

| Ethernet MACs         | N/A         | N/A           | 2 or 4 embedded blocks |

# **Inrush Current**

18

When voltage is initially applied to an FPGA, its internal circuitry undergoes states of ambiguity while configuration storage latches and other circuits are programmed sequentially. The internal contention that occurs during powerup can produce spikes of inrush current that measure in multiple amps. This inrush current often requires the

use of expensive regulators, and larger, more expensive power supplies. To properly configure the FPGA, the power supply must be able to handle the large in-rush currents even if the device operates at much lower dynamic current levels during operation. This is especially true if the clock frequency of the FPGA during normal operation does not push the maximum limits.

Xilinx eliminated nearly all inrush current in Virtex and Spartan series FPGAs a few years ago by embedding innovative *housekeeping circuitry* to prevent this contention from occurring.

# Power Estimations

The heat of competition in the FPGA marketplace can sometimes make it difficult for customers to obtain objective, fair-handed assessments of performance and power claims. So how does one determine which high-performance 90 nm FPGA family consumes the lowest total power, including static and dynamic power measured at the design's operating temperature?

In an attempt to keep a level playing field and the comparisons on an apples-to-apples basis, the Xilinx Web Power Tool v4.1 based on extensive characterization data was used to estimate power for the Virtex-4 devices. Altera's PowerPlay 2.1 power estimation tool was used to do the same for relatively equivalent logic density Stratix II parts.

To keep the static power comparison simple, only the core voltage supply is examined. Temperature invariant auxiliary voltage supplies ( $V_{CCAUX}$  and  $V_{CCPD}$ ) are intentionally excluded. Stratix II FPGAs require additional voltage supply rails and power for every PLL used – these are also not included in the comparison.

If a hard IP block is available in Stratix II, it is used in the comparison; if not, the equivalent soft IP, using the logic utilization published for Stratix II implementations, is used. Because Virtex-4 FPGAs have more hard IP functions than Stratix II, and each hard IP function has more programmable features and options than Stratix II, it is difficult to compare "equivalent" functions; however, the comparison was executed on as much of an "apples-to-apples" basis as driven by the products.

The following results are offered for consideration, and since both tools are readily available, everyone is encouraged to perform the same or similar comparisons themselves. The results are compelling.

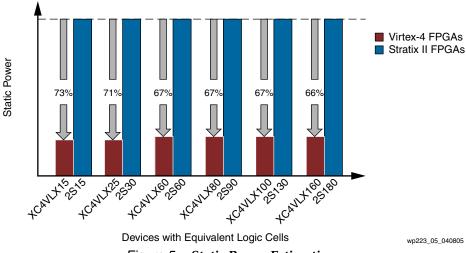

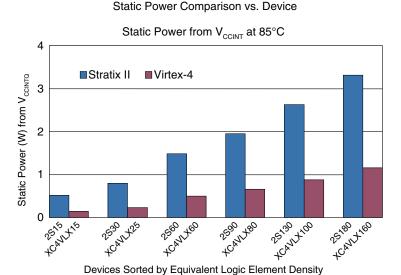

# 66% - 73% Less Static Power

Figure 5 compares the static power at  $T_i = 85$ °C using Xilinx WPT v4.1 vs. Stratix II PowerPlay v2.1. Table 4 shows the detailed data.

Figure 5: Static Power Estimations

# **Hard IP = Less Dynamic Power**

Figure 6 compares the dynamic power at  $T_j$ =85°C using Xilinx WPTv4.1 vs. Stratix II PowerPlay v2.1. Table 5 contains detailed information.

Figure 6: Dynamic Power Estimations

# **Measured Results**

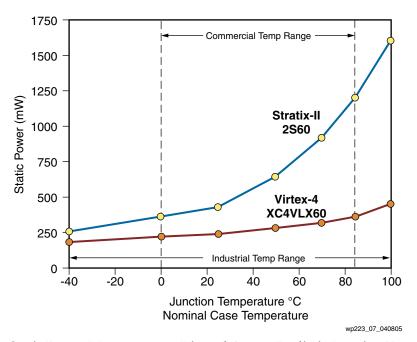

Recognizing the variability encountered when using *power estimators* as new characterization data becomes available from the vendor, Xilinx conducted static power tests on equivalent parts across the full commercial temperature range – an important consideration for many applications.

At a typical operating temperature of 85°C, Virtex-4 devices consume one-fourth the static power of Stratix II – a comparative relationship that remains constant as the temperature increases to 100°C (Figure 7).

Figure 7: Static Power Measurements Viewed Across Realistic Junction Temperature Ranges

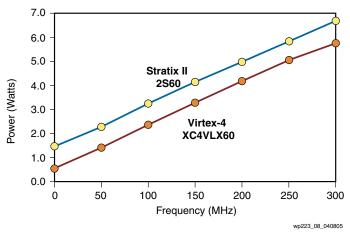

The measured results of the dynamic power tests demonstrate equivalent dynamic power consumption (Figure 8) for Virtex-4 and Stratix II devices when looking at just

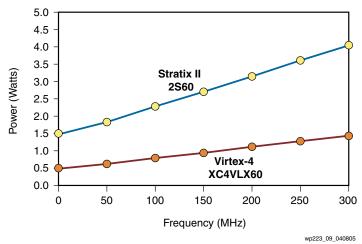

LUTs and FFs. A more dramatic result (Figure 9) is obtained when testing block RAM configurations of equivalent sizes. In large part, the difference is due to the availability of optimally sized 18K bit memories from Xilinx. The smaller Stratix II 4K bit block RAMs consume nearly the same amount of power as the Virtex-4 18K bit block RAMs. Most customer designs either need ultra-small distributed RAM or medium-level memories built using 18K bit blocks – prompting Xilinx to move from 4K bit memories three product generations ago.

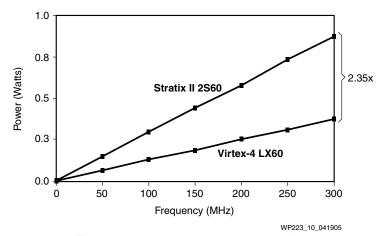

Although Stratix II FPGAs also have DSP blocks that can be connected using adder trees built out of logic resources, the Virtex-4 XtremeDSP slice provides the unique advantage of cascading multiple slices without additional logic. For many DSP functions, this gives a big advantage on speed and power. To test the dynamic power for DSP designs, a 64-tap FIR filter is used. The filter has 63 section asymmetrical taps with 18-bit data stream and fixed 18-bit coefficients. The Virtex-4 FPGA uses 63 XtremeDSP slices in a single column; one slice is used for stimulus. The Stratix II FPGA uses four tap sections in each DSP block, which are added together using nine 3-input adder tree structure. Stratix II ALMs are used for stimulus. Figure 10 shows the Virtex-4 FPGA consuming 2.35x (or 60%) lower dynamic power than Stratix II for DSP designs.

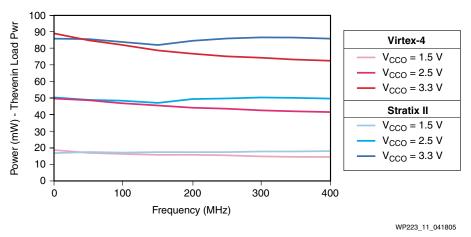

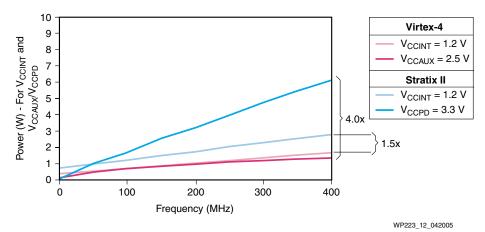

The more astonishing result is found for the  $V_{CCINT}$  core voltage and the  $V_{CCAUX}$  (2.5V) in the Virtex-4 device and the  $V_{CCPD}$  (3.3V) supply in Stratix II. The  $V_{CCAUX}$  in the Virtex-4 FPGA is used for configuration memory (some in DCMs, and some in I/O pre-drivers). The  $V_{CCPD}$  supply in Stratix II is used for configuration and I/O pre-drivers. In order to test I/Os, 500 LVCMOS I/Os were tested at all voltage levels (1.5V, 2.5V, and 3.3V). All outputs are in DDR mode, and loads are terminated to ½  $V_{CCIO}$ . DC to 400 MHz frequency range was used. Shown in Figure 11, the Virtex-4 device consumes lower power at all voltage levels.

In Figure 12,  $V_{CCPD}$  supply consumes four times the power of the  $V_{CCAUX}$  supply — translating into Watts of power difference! The  $V_{CCINT}$  supply in Stratix II also consumes three times the static power and 50% more dynamic power

The conclusion about the tests is that the Virtex-4 device consumes much less power than Stratix II.

# **Dynamic Power - Fabric**

Figure 8: Fabric Test with 25,000 LUT/ALUTs and 21,000 FFs (High Toggle Rate). All measurements were taken at  $T_i = 85^{\circ}$ C.

# **Dynamic Power - Memory**

Figure 9: FIFO/Block RAM test with 252 M4K in Stratix II and 63 Block RAM in Virtex-4 FPGAs (same total storage). All measurements were taken at  $T_i = 85^{\circ}$  C.

# Dynamic Power - DSP (64-Tap FIR Filter)

Figure 10: DSP Test: 64-Tap FIR Filter

# Dynamic Power - I/O .

Figure 11: Virtex-4 FPGAs Consume Less Power at All Three V<sub>CCIO</sub> Voltages

Figure 12: I/O Test: Stratix II shows 1.5x the  $V_{CCINT}$  Dynamic Power and 4x the  $V_{CCPD}/V_{CCAUX}$  Power compared to the Virtex-4 FPGA

Total Power Budget Comparison

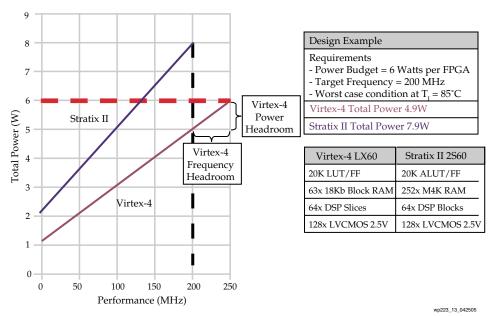

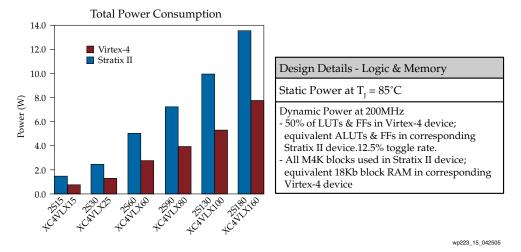

Another simple way to obtain a high-level comparison of power consumption in FPGAs is to assess the available performance and power headroom for a given power budget and target frequency. For this comparison, popular applications for high-performance FPGAs at a sweet-spot density of 60,000 logic cells were considered, e.g., multi-service provisioning platforms in networking and telecom access markets; blade servers in storage and server markets; line cards in wireless base stations; and control cards in industrial and military/aerospace systems. Operating at an average target frequency of 200 MHz, with operating temperatures in the range of 65-100°C, the power budget for these applications is typically 6W per FPGA.

Using these applications as an example, the Virtex-4 FPGA meets the target frequency, well within the power budget at 4.9W. On the other hand, Stratix II FPGAs exceed the power budget, consuming 7.9W at the target frequency. Consequently, when constrained by the 6W power budget, Stratix II delivers only 133 MHz performance (Figure 13).

Figure 13: Customers Select the High-performance FPGA that Best Meets Their Power Budget

Xilinx Telecom Customer's SPI4.2 Design Comparison

24

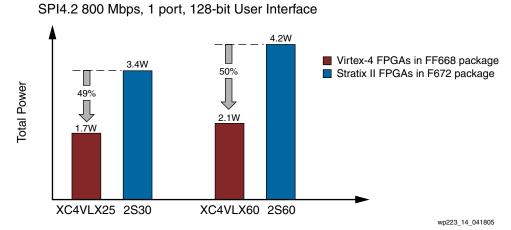

Intrigued by the power consumption advantages in Virtex-4 devices, one Xilinx customer used the web power estimation tools to compare the power consumption for a SPI4.2 core implemented on Stratix II and Virtex-4 FPGAs.

The Optical Internetworking Forum's SPI4.2 parallel interface appears in numerous 10-Gb/s networking and telecom applications. Because virtually all networking and telecom equipment has stringent power and thermal budgets, the customer was pleased to discover that the estimators showed Virtex-4 devices consuming 50% lower total power than Stratix II for this application.

Satisfied but surprised by the results, the customer decided to perform real measurements on actual implementations to verify the findings. Once again, this time with actual lab results in hand, the customer found that Virtex-4 FPGAs consumed 50% lower total power for the SPI4.2 implementation than did the Stratix II version.

The Xilinx customer's test has been recreated using similar conditions, with similar results. The results are presented in Figure 14 and Table 3.

Figure 14: Customer Analysis on SPI4.2 Power Consumption

Table 3: Virtex-4 vs. Stratix II Implementation

|                              | Virtex-4 Implementation                                                                                                                   | Stratix II Implementation                                                                                                              |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Protocol                     | SPI4.2 v7.2, 800 Mb/s                                                                                                                     | SPI4.2 v2.2.2, 800 Mb/s                                                                                                                |

| User I/F                     | 128-bit, 1 port                                                                                                                           | 128-bit, 1 port                                                                                                                        |

| Logic                        | 3750 Slices:  • 4893 LUTs  • 25% toggle rate used                                                                                         | Tx and Rx:  • 10844 ALUTs (calculated from 10968 + 2588 LEs)  • 25% toggle rate used                                                   |

| Memory                       | 306 Kb total – 17 18Kb-block RAMs used:  • 13 - 512 x 36  • 2 - 36 x 512 write and 18 x 1024 read  • 2 - 1024 x 9  • 25% toggle rate used | <ul> <li>244 Kb total – 62 block RAMs used:</li> <li>61 - M4K blocks</li> <li>1 - M512 blocks</li> <li>25% toggle rate used</li> </ul> |

| LVDS                         | <ul><li>17 LVDS pairs for Rx and Tx:</li><li>35 pF average load</li><li>Additional differential clock output</li></ul>                    | <ul><li>17 LVDS pairs for Rx and Tx:</li><li>35 pF average load</li><li>Additional differential clock output</li></ul>                 |

| Clock Frequency (Assumption) | 200 MHz single clock                                                                                                                      | 200 MHz single clock                                                                                                                   |

**Note:** Limited data available on the Stratix II implementation. For fair comparison, some assumptions had to be made about clocks. See Answer Record 20430 on Xilinx.com for Virtex-4 SPI4.2 power.

# 1 to 5 Watts lower power per FPGA

Having demonstrated substantial power savings – both in static power as a result of triple-oxide technology and in dynamic power using embedded IP – and having presented corroborating results from both power estimators and lab measurements using various designs, one might well ask, "What does it all mean for my design?"

The simplest example provides the best perspective. Using an equivalent amount of generic logic and memory in Virtex-4 and Stratix II devices of equivalent density, with no consideration of other embedded IP, the Virtex-4 FPGA saved 1 - 5W in power. A design should realize at least this much power savings per every Virtex-4 FPGA used, if not better. The results are shown in Figure 15. To present the lowest bar in power savings, benefits from extensive hard IP in Virtex-4 FPGAs were not included.

Figure 15: Virtex-4 Designs Consume 1 to 5 Watts Lower Power per FPGA

# **Power Struggle**

The battle to deliver maximum performance with minimum power expenditure has taken center stage in the evolution of the FPGA. Power conservation impacts every budget, whether technological or financial. Product acceptability, reliability and profitability depends as much or more on power efficiency as it will on performance.

Virtex-4 FPGAs not only have a far superior feature set, but also exhibit a real power consumption advantage. The choice should be very clear for designers who require lower power consumption, and high-performance and functionality. Initial test results tell the story:

- Up to 73% lower static power with the industry's first triple-oxide technology

- Up to 86% lower dynamic power with high-performance embedded IP

The competition in the market does not end with 90 nm devices. Some interesting new dynamics arise when moving into a 65 nm node and below. Fortunately for Xilinx, one inherent value of using triple-oxide technology is that it scales nicely with each new process.

As for the value of embedding hard IP wherever appropriate, it is practically an industry axiom. Xilinx has incorporated the right amount of programmable embedded IP with programmable logic to make the whole solution more flexible with higher-performance, and lower power. In the long term, customers will use only Platform FPGAs that provide the best of performance and power.

# **Appendix**

26

# **Static Power Comparison Data**

Table 4 gives the comparison data for static power.

| Virtex-4 St     | atic Power                  | Stratix II Static Power |                             | Virtex-4 Power                 |

|-----------------|-----------------------------|-------------------------|-----------------------------|--------------------------------|

| Virtex-4 Device | Typical 85°C T <sub>j</sub> | Stratix II Part         | Typical 85°C T <sub>j</sub> | Reduction<br>Typical 25°C/85°C |

| XC4VLX15        | 138 mW                      | 2S15                    | 515 mW                      | 73%                            |

| XC4VLX25        | 231 mW                      | 2S30                    | 792 mW                      | 71%                            |

| XC4VLX60        | 493 mW                      | 2S60                    | 1,478 mW                    | 67%                            |

| XC4VLX80        | 640 mW                      | 2S90                    | 1,960 mW                    | 67%                            |

| XC4VLX100       | 863 mW                      | 2S130                   | 2,630 mW                    | 67%                            |

| XC4VLX160       | 1,117 mW                    | 2S180                   | 3,310 mW                    | 66%                            |

Table 4: Static Power Comparison Data

- Core static power =  $I_{CCINTQ}$  x  $V_{CCINT}$ . Altera data is based on PowerPlay tool v2.1 on www.altera.com. Static power for  $V_{CCPD}$  (the Stratix II  $V_{CCAUX}$  supply) and  $V_{CCIO}$  does not change with temperature and is not shown. Stratix II also consumes additional power for PLL supply rails that are not shown.

- Devices of equivalent logic density are compared.

# **Dynamic Power Comparison Data**

Table 5 gives the comparison data for dynamic power.

Table 5: Dynamic Power Comparison Data

| Virtex-4 Dynamic Po<br>(Room Temperatus                                                                                | Strativ II Livnamic Power (Koom Jemn) |                                                                                                         | Stratix II Dynamic Power (Room Temp) |       |

|------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------|-------|

| Function at 200 MHz                                                                                                    | Power                                 | Function at 200 MHz                                                                                     | Power                                |       |

| <ul><li>1 LUT and 1FF</li><li>30% toggle rate</li><li>Medium Routing</li></ul>                                         | 0.15 mW                               | <ul><li>1 ALUT and 1 FF</li><li>30% toggle rate</li><li>Routing data unavailable</li></ul>              | 0.15 mW                              | ~same |

| <ul> <li>1 XtremeDSP™ Slice</li> <li>18x18 MAC</li> <li>Registered in/out</li> <li>Medium (55%) toggle rate</li> </ul> | 6.6 mW                                | <ul> <li>1 DSP Block</li> <li>18 x18 MAC</li> <li>Registered in/out</li> <li>50% toggle rate</li> </ul> | 8.57 mW                              | 23% ↓ |

| PowerPC™ Processor  • 16Kb I-Cache and D-Cache  • 2 DCMs                                                               | 120 mW                                | Soft Processor • 1 - 6K I-Cache and D-Cache                                                             | 879 mW                               | 86% ↓ |

| <ul> <li>18 Kb block RAM</li> <li>Width = 18, Depth = 1</li> <li>50% read and 50% write</li> </ul>                     | 6.16 mW                               | Equivalent M4K RAM  • Width = 18, Depth = 1  • 50% read and 50% write                                   | 33.98 mW                             | 82%↓  |

| Ethernet MAC - embedded • 1 Gb/s, 125 MHz                                                                              | 27 mW                                 | Ethernet MAC - soft  1 Gb/s, 125 MHz  2500 ALUTS and 2500 FFs                                           | 160 mW                               | 83%↓  |

# **Power Across the Board**

# Optimize Design of Xilinx FPGA, ASIC, and Point-of-Load Power Applications

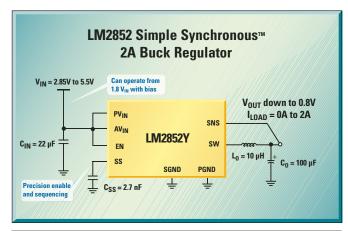

# LM2852 Features

- Best-in-class 60 m $\Omega$  switches provide over 95% efficiency

- Factory-programmable EEPROM for any output voltage between 0.8V to 3.3V

- Up to 1.5 MHz internal compensation eases designing with a variety of output capacitors

- Available in thermally enhanced, ETSSOP-14 package

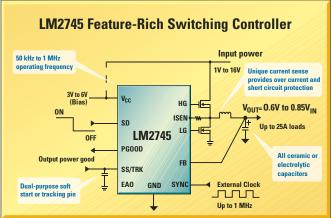

# LM2745 Features

- Output voltage adjustable down to 0.6V

- Switching frequency from 50 kHz to 1 MHz

- Startup with a pre-biased load prevents sagging of output

- Available in a TSSOP-14 package

Ideal for FPGA/DSP applications in networking, telecommunications, enterprise, and automated test and measurement applications

For free samples, evaluation boards, datasheets and online design tools, visit us today at:

power.national.com

Or call 1-800-272-9959

August 2005

# Static Power and the Importance of Realistic Junction Temperature Analysis

By: Matt Klein

Total power consumption of a board or system is important; each FPGA or ASIC in a system is beginning to be forced to meet a power budget. With this concern and the trend of increasing static power with use of high performance 90 nm FPGAs, Xilinx has put considerable effort into reducing static power in the Virtex™-4 FPGAs. To this end, it is consider realistic to a operating important temperature for the FPGAs, which can easily have junction temperature up to and in excess of 85°C. As junction temperature rises, static power rises exponentially, fueling this concern.

29

# Introduction

Customers expect FPGA and ASIC vendors to reduce cost and increase performance. Typically, this was achieved in the past by reducing transistor sizes, hence increasing the performance and decreasing the die area and cost.

Reducing transistor sizes increases transistor leakage current, and therefore static power. With 90 nm technology in FPGAs or ASICs, there is a particular challenge to reduce static power. A further problem is that leakage rises dramatically with junction temperature. This white paper describes where static power comes from and its variation with temperature, providing insight into how Virtex-4 FPGAs address decreasing static power. Xilinx leverages its vast experience as the industry leader, producing millions of 90 nm FPGAs, to research this issue and consequently reduce power in 90 nm Virtex-4 FPGAs.

Even though system speeds are increasing, core voltage is dropping, which reduces the rate of increase of dynamic power; however, static power is growing exponentially over time as we move to smaller and smaller technology nodes because of increasing transistor leakage. Figure 1 from the International Technology Roadmap for Semiconductors (ITRS) shows a cross-over point as the industry arrives at 90 nm and smaller technology nodes, where static power is beginning to eclipse dynamic power for many applications.

Figure 1: Static and Dynamic Power vs. Technology Node

# Decreased Power Lessens Other System Design Issues

30

FPGAs are being used increasingly in many applications, so reducing power consumption in FPGAs provides huge benefits to the system design. Some of the key benefits are shown below:

- Fewer thermal concerns lower power causes smaller rise in junction temperature, preventing thermal runaway:

- Use smaller heat sinks or no heat sinks at all.

- Allow for a simpler system thermal design requiring less airflow and smaller or fewer fans.

- Lower cost power system reduced power requires smaller power supplies:

- Power supplies cost from \$0.50-\$1.00/Watt.

- Additionally, there are some *total power* system considerations where it is important to stay below a step function jump, such as < 500 W, < 1 KW, etc. If the design is at the border, every watt counts.

- A smaller and simpler power circuitry means:

- Fewer components.

- Smaller PCB.

- Higher system reliability running with reduced power lowers the junction temperature, and lower junction temperature improves reliability.

Since total power consumption of a board or system is important, each FPGA or ASIC in a system must meet a power budget. Users need to design within the power budget while being pushed to higher performance and lower cost - a rather difficult challenge at 90 nm. With this in mind, Xilinx has put considerable research and development into reducing static power in the Virtex-4 FPGAs and actually reversed the trend for high static power in a high performance 90 nm FPGA.

Where Does Leakage and Static Power Come From? A well-known rule of semiconductor physics is that when transistor length decreases, leakage current increases. Smaller physical distances make it easier for current to leak. Both source-to-drain leakage and gate leakage are inversely proportional to channel length and gate oxide thickness, respectively, and show a dramatic increases in leakage. Static power is the power consumed due to leakage in the transistors even when the transistors are not switching. Therefore, power is consumed in the FPGA even when it isn't performing a task.

The leakage is dramatically influenced by junction temperature. This is why it is important to look at realistic junction temperatures for the FPGAs in the system to properly account for static power. Figure 2 shows the dramatic increase in I<sub>CCINTQ</sub>, the leakage or static current for the core transistors in the FPGA.

Figure 2: Leakage Current vs. Temperature for 90 nm Virtex-4 Devices

Two components contribute to leakage:

• Source-to-Drain Leakage: This current flows from source to drain of the transistor, even when the transistor gate is off. When the transistor gets small, it is harder to prevent this current from flowing, and therefore, 90 nm transistors tend to exhibit

source-to-drainage leakage with much greater magnitude than larger transistors, all parameters being equal. The other problem is the thickness of the gate oxide. A thinner oxide allows the transistor to be switched on and off faster, but it also increases leakage. The amount of leakage is also influenced by the threshold voltage of the transistor. The threshold voltage, or  $V_T$  of the transistor, is the voltage between the gate and the source at which the channel conducts current to a certain extent. Small high-speed transistors need a lower threshold voltage (influenced by oxide thickness and doping) to maintain the speed with which the transistor can be turned on and off via gate control, but this also tends to increase the leakage because the channel of the transistor can not be turned off completely. The goal is to make fast transistors, but unfortunately, physics is against this. Another important note is that source-to-drain leakage increases exponentially with increasing temperature; in going from a junction temperature ( $T_J$ ) of 25°C to 85°C, it goes up by a factor of 5x (see IS  $\rightarrow$  D, Figure 3, page 4).

• Gate Leakage: This current flows from gate to substrate. This component of leakage is now more substantial as transistor gate oxide thickness has decreased at the 90 nm technology node. At room temperature, the leakage from gate to substrate is larger than the source-to-drain leakage in the 90 nm fast thin oxide transistors; however, unlike source-to-drain leakage, this gate leakage only increases marginally with increased temperature (see I<sub>GATE</sub>, Figure 3).

# Static Current Components Leakage Components vs. Junction Temperature CCINTQ Gate Drain Source IS→D Leakage I<sub>ccinto</sub> $I_{CCINTQ} = IS \rightarrow D + I_{GATE}$ -20 40 20 80 100 120 140 Junction Temperature

Gate Leakage Dominant at 25°C, Source to Drain Dominates at High Temperature  $^{\circ}$

Figure 3: Leakage Current Components versus Temperature for the 90 nm Virtex-4 FPGA

The net effect is that total leakage  $I_{CCINTQ} = IS \rightarrow D + I_{GATE}$  goes up by 2x - 3x between  $25^{\circ}C$  and  $85^{\circ}C$ .

FPGAs and ASICs are getting larger and larger due to requirements of hardware and system designers. This means that with parts the size of the new Virtex-4 LX200, there are upwards of one billion transistors to worry about. A leakage of 10 nA per transistor amounts to a leakage of 10 A!!

There is a silver lining for FPGA manufacturers that is not applicable to ASIC manufacturers: Xilinx has solved the issue of high static power in the Virtex-4 device, a high performance 90 nm FPGA, by using triple-oxide.

What is Triple-Oxide and How Does It Affect Static Power Triple-oxide simply means that we use a third thickness of gate oxide in making some of the transistors in the FPGA (two oxide thicknesses are used in devices like the Virtex-II Pro FPGA). Most transistors in the past had a thin oxide layer, some with NMOS or PMOS transistors that operate at either low  $V_T$  or regular  $V_T$ . Thick-oxide transistors are mostly used for I/O drivers.

Oxide deposition thickness is a very stable and controllable process in the semiconductor industry because it depends on temperature, concentration, and exposure time. Figure 4 shows the Virtex-4 transistor with the middle oxide thickness used in the triple-oxide process. The oxide thickness is still very, very thin, but this thicker oxide transistor has much lower leakage than the standard thin-oxide low  $V_T$  and regular  $V_T$  transistors used in Virtex-II Pro FPGAs and in various parts of Virtex-4 FPGAs.

Industry's First 90 nm Triple-Oxide Technology

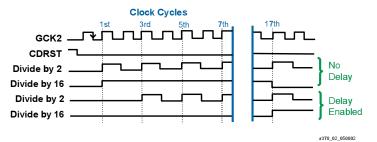

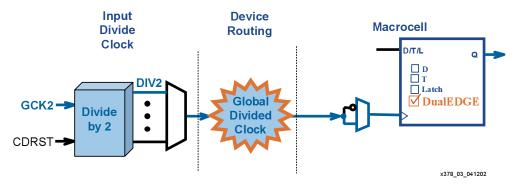

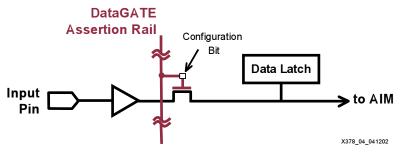

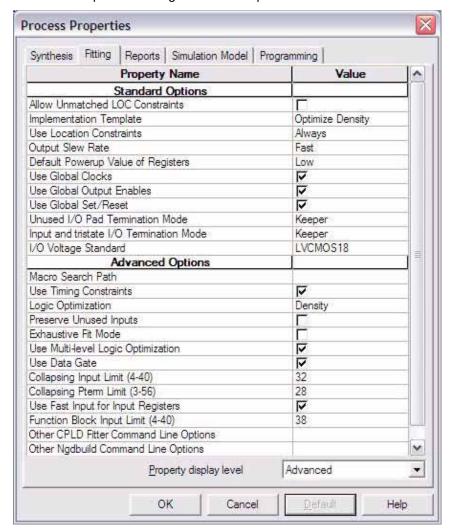

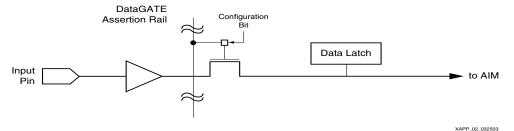

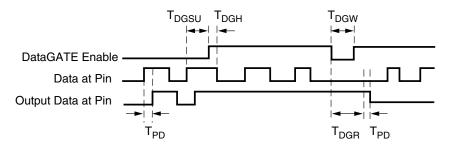

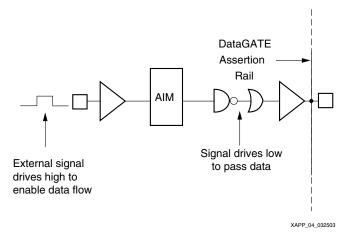

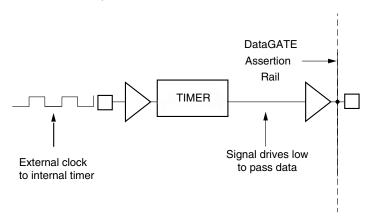

Only Xilinx FPGAs Benefit From This Technology